DAC34H84的时钟DDR的下降沿采不到数,怎么办?需要在哪里设置吗?

DAC34H84的TI官方开发板。

用FPGA在时钟的上升下降沿的时候放上数(用示波器看眼图和时钟的关系绝对满足setup和hold time时间关系),但是始终只有上升沿的数能从IOUTA和IOUTB模拟口出来,IOUTA和IOUTB始终是一样的,这是怎么回事?

不应该是IOUTA出的是上升沿采的数转换的而IOUTB是下降沿采的转换的吗?

莫非需要在哪里设置?

DAC34H84在电路中有个8 sample FIFO模块,所以数据输入和ADC核心工作可以不是同一个频率的。数据输入的确是DDR的,在上升沿下降沿都有数据输入。建议观察下DATACLK 和DACCLK的频率。可以试着将FIFO模块bypass调试,谢谢

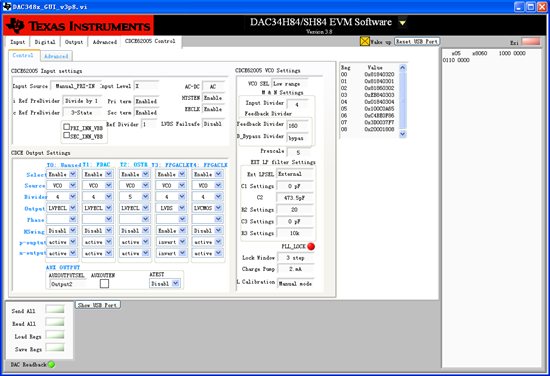

本来就没有用FIFO,FIFO是disable的啊,DATACLK是100MHz,DACCLK是200MHz。相位上有固定关系,这个相位是由开发板上的CDCE6005控制的,应该是没有问题的啊。

你好,一个sample写完需要2个dataclk周期,而dacclk只在每个周期的上升沿捕获整个sample,所以我觉得你的dataclk需要是dacclk的两倍,你可以看下datasheet中的word-wide format和byte-wide format的描述,谢谢

更正下:一个sample写完需要1个dataclk周期,而dacclk只在每个周期的上升沿捕获整个sample,所以dataclk需要和dacclk相同,你可以看下datasheet中的data format的描述,谢谢

还是不行啊,周期设成一样的也不行,我现在是上升沿的数据是一个正弦波,下降沿是0。但是怎么调整时钟频率和相位关系,IOUTA和IOUTB始终是一样的,连噪声的波形在示波器上看都是一样的。

我是这样实现的,FPGA产生两个时钟clk100MHz0和clk100MHz180,然后分别在其上升沿放数(便于测试,我clk100MHz0放的是一个正弦波,clk100MHz180放的是0),然后DATACLK是clk100MHz90,这样的时候IOUTA和IOUTB都输出的是我clk100MHz0的波形。

如果调整DATACLK的相位,IOUTA和IOUTB的输出一起动,时钟一样。

DACCLK时钟变成100MHz,IOUTA和IOUTB的输出也是一起动。

感觉上就像是IOUTA和IOUTB是同一个沿采的一样,因为在示波器上看两个波形就像是同一个波形。

确信我没有犯 像把示波器探头放在 同一个位置 或者同一个信号上 的错误。

一点小建议

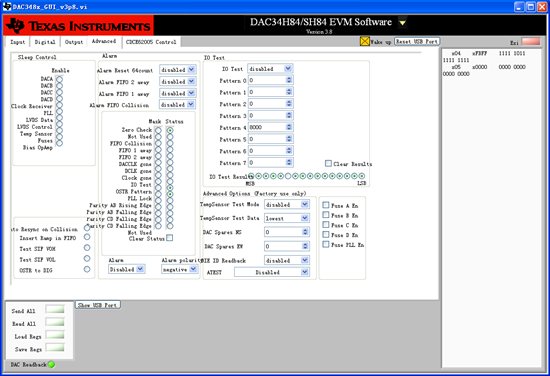

先设置寄存器,把内部的常数数据源和NCO或者Mixer打开,看一下输出的结果是不是正常。

然后启用IQtest功能,看看寄存器里是不是有告警。

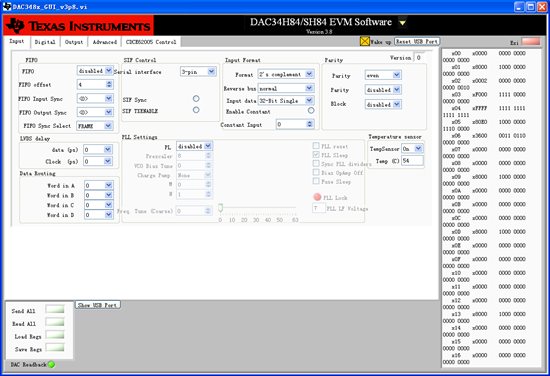

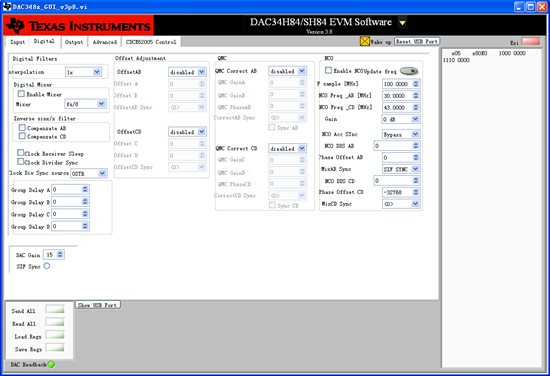

我的设置是这样子的

IOTest使能的话 结果那一行的灯全亮

Data routing是不是有点问题。好像是把数据都放到一个口了。

读一下IOtester对应的寄存器,看看是不是有错误。如果有错误就说明接口有问题

Data routing 改成别的也是一样的,没什么效果,(开mix的时候Data routing是有效果的,可以看到IOUTA和IOUTB有区别),IOtest总是失败(读寄存器的话pattern肯定是写进去了,但是iotest_results都是1,也就failed)。

我给DAC的只有DACCLK 100MHz,DATACLK 100MHz90,DATA,板子上没有画ISTRP和SYNC,与这个有没有关系呢?

当时考虑是不用FIFO的,貌似这两个信号如果不用FIFO的话应该是没有啥用的。

建议开启FiFO功能试下,看下这个问题能不能解决,谢谢

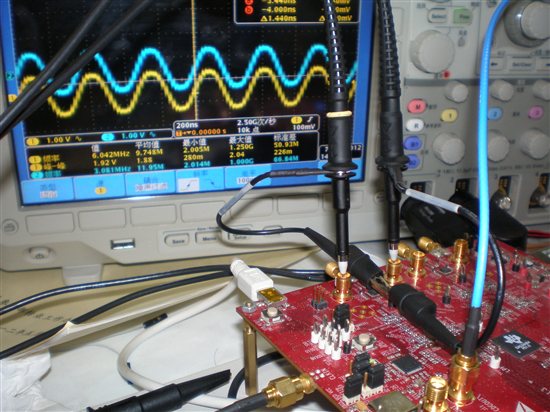

这是实际测试波形:DATA和DATACLK(上升沿有数,下降沿数为0)

这是IOUTA和IOUTB的波形:

哈哈,问题解决了,多谢多谢大家。

原来还真是Data routing的问题,关键在于它有两个Data routing的控制器,一个在Input,一个在output,两个必须对应起来设置才行,我原来的都设的不对。

太麻烦大家了,抱歉,谢谢谢谢!

太谢谢大家了,问题解决了。

原来还是Data routing的问题,关键在于它有两个Data routing控制器,一个在Input,一个在Output,两个必须配合着使用才行。

谢谢大家谢谢!

王

很高兴能帮到你。还是请你测试一下IQtester功能,因为以后你在速率提升以后,可能会遇到误码上升的情况