ADS828高频采样

时间:10-02

整理:3721RD

点击:

使用ADS828采集模拟信号,随着CLK的提高,采集到的数据会有一些毛刺。不知道怎么解决。

我是用Actel的FPGA控制的,ADS828的时钟也由FPGA发出。ADS828控制在工作状态和低功耗状态。

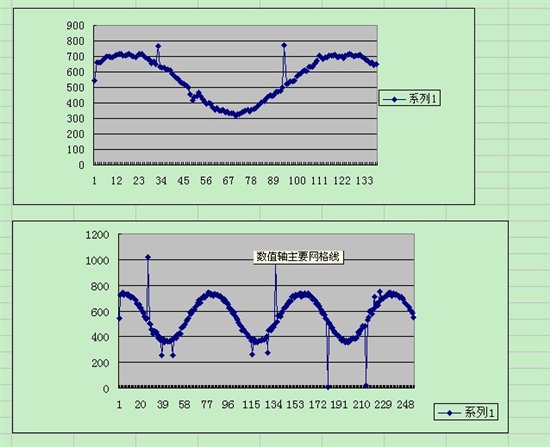

我测试了10MHZ,16MHZ,32MHZ,48MHZ的CLK,模拟信号为1MHZ,峰峰值小于800mv的正弦波。

但是在16MHZ,采集到的波形,很不好;32MHZ,,48MH出现坏点;10mHZ的波形正常。

应该是FPGA在抓取数进行数字域处理的时候没有满足datasheet第4页上的时序关系,采样率越高,FPGA端时序越紧张,越有可能无法满足时序要求,出错概率就如你所测的变大。谢谢!

Yingzi Liu

ADS828的时钟不建议有FPGA供给,这样性能很不容易保证。建议由专业的时钟芯片供给。比如CDCE72010,CDCM7005等。而且由FPGA供时钟的时候,时钟和数据之间的时序在高速时不宜满足