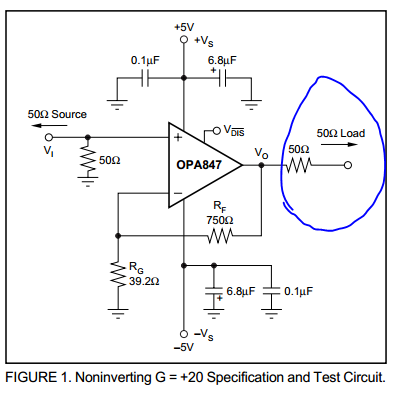

为什么运放输出端一般会串一个50欧姆电阻,然后又会接一个50欧姆的负载到下一级了?

求解:为什么运放输出端一般会串一个50欧姆电阻,然后又会接一个50欧姆的负载到下一级了?

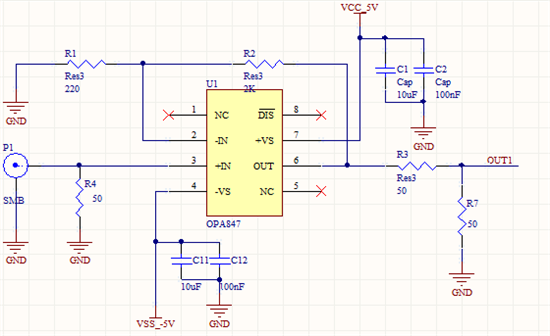

如上图可不可以直接去掉R3,然后用R7进行阻抗匹配?另外R3的作用是什么?

R3匹配的是传输线的阻抗,消除反射

非常感谢,另外那请问一下,布线的时候R3是不是要靠近前一级运放的输出脚?

是的,尽量靠近运放输入端,减少输出端因为PCB走线引入的寄生电容

手册中有对此说明:

The Typical Characteristics help the designer pick a recommended RS versus capacitive load. The resulting frequency

response curves show a flat response for several selected

capacitive loads and recommended RS combinations. Parasitic capacitive loads greater than 2pF can begin to degrade

the performance of the OPA847. Long PCB traces, unmatched cables, and connections to multiple devices can

easily cause this value to be exceeded. Always consider this

effect carefully and add the recommended series resistor as

close as possible to the OPA847 output pin (see the Board

Layout section)

非常感谢,基本上明白了。

好的,有什么问题再发帖讨论吧

你好,我想问一下这个电阻的大小怎么决定?

亲;按线路特征阻抗确定。

那对于低频的信号传输需要阻抗匹配吗

只有频率高到传输距离与波长相比拟时,才存在阻抗匹配的问题。另外如果是容性负载,输出端的电阻是为了抑制震荡

请问R7和R3一般在电路中都需要的吗,R7是什么作用呢?

R7在这里是负载电阻。

这里的R3是否也是电路的输出阻抗?

r3对于闭环输出可以看做是负载。

但是这里应该把它看做是输出电阻,与接收端(负载)进行阻抗的匹配。

我想问下,R3和R7形成阻抗匹配,那么传输线的阻抗匹配又怎么解释呢

这英文不是写着越靠近opa847越好吗,为什么楼上说越靠近下级输入端越好?

应该是笔误,R3是应该靠近输出引脚,但R7应该是不需要的吧,就像第一张图那样