运放参数的详细解释和分析-part20,建立时间(Settling Time)

相信关注运放建立时间的人不是特别多,但是运放的建立时间,对于其后的ADC至关重要。如一个16bits的ADC,它的一个LSB对应的电压范围是其满量程的15ppm, (百万分之十五) 。如果驱动ADC的运放还没有达到最终的值就被ADC采样了。这必然会引起ADC的采样误差。

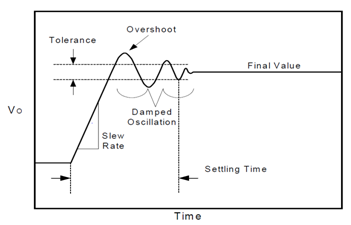

放大器的建立时间是当运输入为阶跃信号时,运放的输出响应进入并保持在规定误差带所需的时间。这个误差常见的值为0.1%, 0.05%,0.01%。一个杯具的时,误差大小与建立时间不是线性关系。如误差0.01%的建立时间可能是误差0.1%的建立时间的30倍以上。神奇吧。下图是运放的建立时间的示例说明图,建立时间,就是从阶跃信号开始到信号误差达到目标值的这段时间。如图上可以看出,运放运阶跃信号的响应会是一个含有过冲和振铃的二阶响应。这个响应看上去很熟悉,像控制系统的二阶响应。所以以下的分析与控制系统有相似性。

运放的建立时间,主要有两段组成,第一段是运放的输出电压从起始值到达目标值附近,这一过程是一个非线性过程。这一段的时长是由给运放的补偿电容充电的电流所决定的。关于这个补偿电压,在运放的压摆率中提到过。因此也可以理解为第一段时间与运放的压摆率有关,(压摆率的决定因素也是运放补偿电容充电的快慢)。第二段时间是指输出已经接近最终目标值了,进入这一阶段后,运放处在准线性区。这一阶段的特性,主要受运放的零-极点对(doublets)影响。在高速运放中,运放的slew rate非常高,因此第一段时间非常短,因此建立时间主要由第二段时间所决定。

关于第二段时间,感兴趣的可以参阅B.Yeshwant Kamath的经典论文

Relationship Between Frequency Response and Settling Time of Operational Amplifiers

关于建立时间的测量方法,可能需要比较精密的电路,和参数良好的仪器。网上也有经典的文章介绍。感兴趣的可以找一下。

Measuring op amp settling time by using sample-and-hold technique

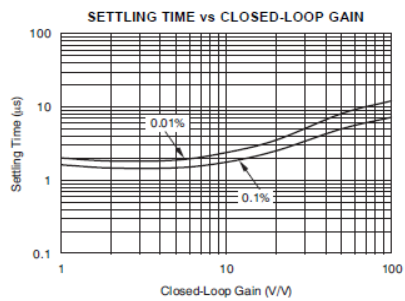

从运放的指标上讲,运放的建立时间会受到大信号参数-压摆率 (SR)的影响和小信号参数-闭环增益的影响。下图是一款运放的建立时间与闭环增益的关系。

通过图表可以看出,随着闭环增益增加,建立时间也随着增加。这是由于高增益时,运放的闭环带宽会降低,因此调整输出误差的环路增益(AolB)也会减小。最终造成放大电路建立时间的增加。

最后再罗嗦一句,对于数据采样保持电路来说,建立时间是非常重要的。尤其对于ADC的输入需要通过multiplexer在不同信号间切换的。一定要注意让信号建立起来后,再进行采样。否则会引起不可预知的误差。

谢谢分享,又学习了,哈哈

-------------------------------

气相色谱仪

第一段是运放的输出电压从起始值到达目标值附近,这一过程是一个非线性过程。第二段时间是指输出已经接近最终目标值了,进入这一阶段后,运放处在准线性区。这两个地方应该互换吧,第一阶段的?U=I/C*?t,应该是一个线性过程。

你好,问一下setting time和ADC的LSB值的重要关系体现在哪,或者说怎么匹配两者

非常感谢