放大器噪声计算

各位麻烦请教个问题:

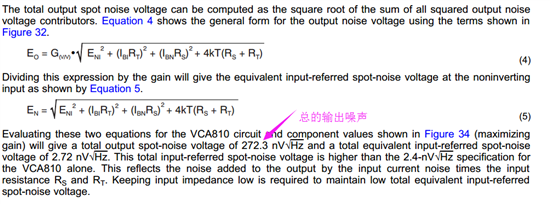

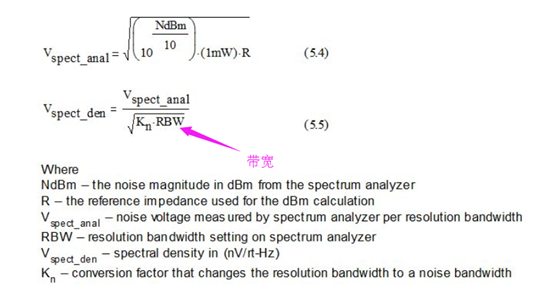

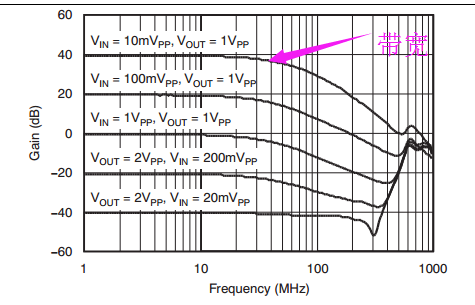

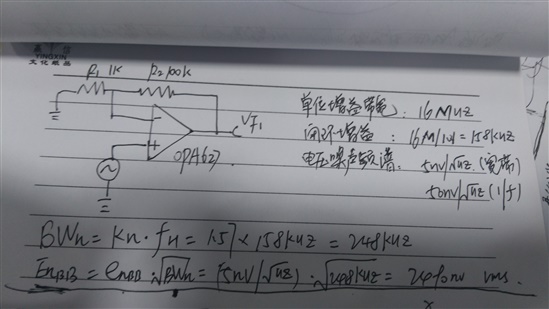

问题是围绕放大器噪声,我在对程控增益放大器VCA810做实验时发现他的数据手册上写的在最大增益下的输出噪声为272.3nv/根号hz(如下面第一幅图片),我想把这个换算为dbm,我在ti的大课堂上看到一个转换公式(如下面第二幅图片),但是在转换时我对里面的带宽不知道如何确定,如果按照数据手册的带宽计算我发现完全不对(如下图3),麻烦大神求解!

第一幅图片

第二幅图片

第三幅图片

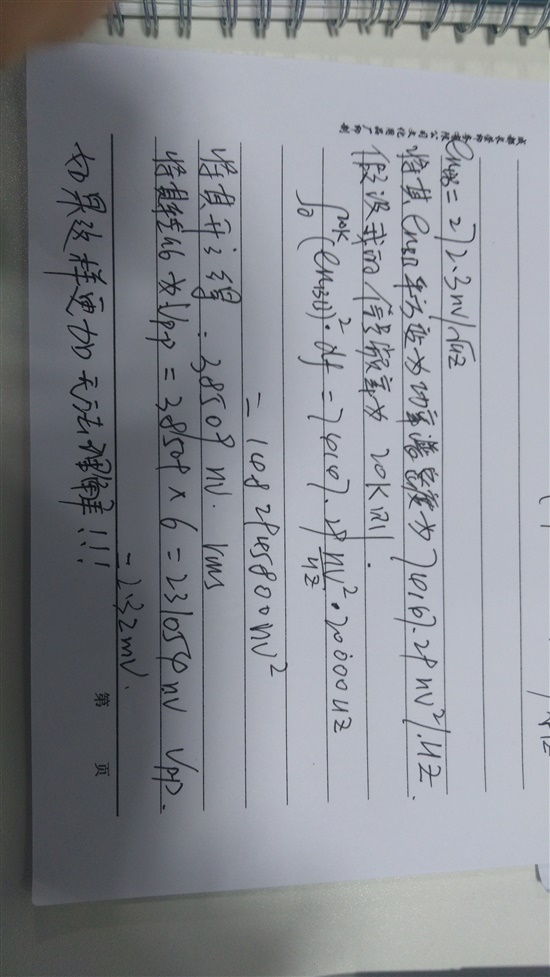

此外我这样大概计算可不可以:

希望得到帮助。。

我对有开环增益的OPA放大器进行计算就可以,但是像VCA810的带宽太大了,没办法算,是不是加个低通选出来一段啊?

运放可以构成滤波电路,带通滤波,等。因此你计算那个带宽肯定不能脱离实际的电路,这也是为何一般不提供dbm为指标的原因吧。

dbm这种单位是功率单位,这里有个隐含条件是在50ohm电阻,可以推导出电压值。

上面的噪声的单位是噪声密度的单位,一般计算噪声的时候都是算出其输入参考噪声再乘以其噪声带宽来算到输入总噪声。

这颗放大器有个特点,带宽不随增益变化,带宽好确定.

在这里如果只是噪声密度的话(nV√Hz)跟带宽没有什么关系。

只有算噪声幅度的时候,需要考虑放大器的带宽,其就可以简单处理为噪声带宽为1.57*30MHZ (一阶低通)

谢谢你的解答!

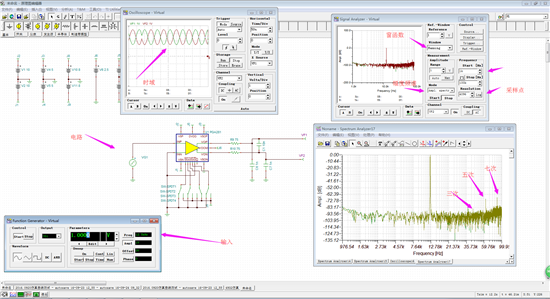

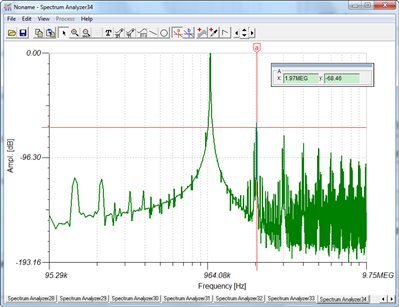

还有就是我仿真想去看一下这个器件的频谱,但是我发现噪低很差,不知道是我没有设置对还是咋了?并且谐波抑制也不好,下面是我的仿真图还有时域、频域图,麻烦你看看。。谢谢啦

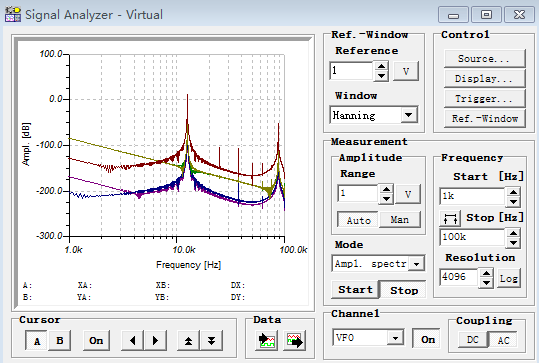

麻烦你帮我解答一下。我用的hanning窗去看的频谱,噪低只有90左右,而且奇次谐波比较大,电路有问题还是?

你好,家里的电脑没有安装TINA,没有办法跟你仿真。 看你的参考是的1V电压, -90db的低噪,也就是换算过来31uV的低噪。

你贴出你的电路,星期一再一起讨论。

首先非常感谢你的回答。

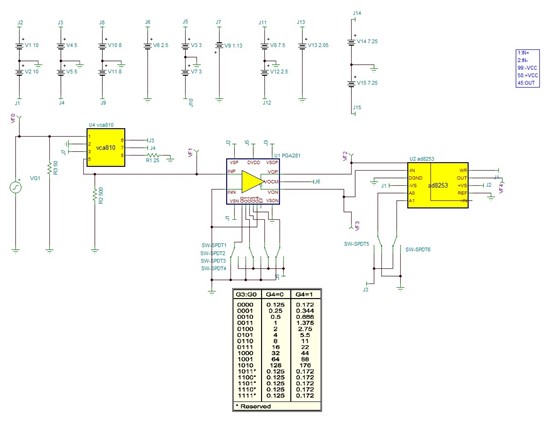

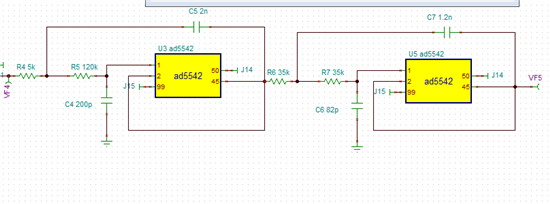

我把电路贴出来一起讨论一下,我再把我的疑问叙述一下:

1、下图1是我的电路,采用第一级VGA芯片VCA810,第二级和第三级都是数控的PGA281和AD8253.因为我要放大的信号幅度不确定,小至0.1mv,大致1v左右吧,信号的频率为12.5K,所以就设计了这样的电路,实物也做出来了。如图1

图1:

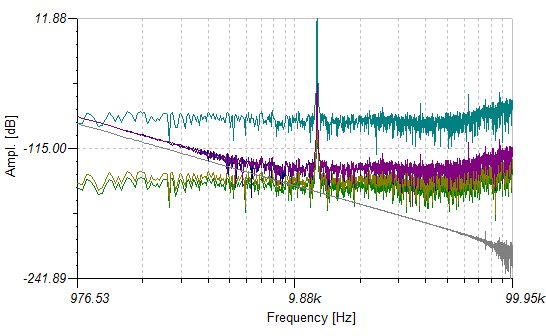

2、在调试实物的时候发现我的噪低很高,只有-60左右,主要是二次和三次谐波很大,感觉没有被抑制,所以就跑来分析计算。因为之前我只是对时域上进行了分析和仿真以及计算,对频域没有经验,麻烦给给点意见。如图2:(调试图片没有拍,发一个仿真的图片)这个还好,实际比这个差多了

3、在这就是对仿真曲线的问题了。

下面图3是我的仿真信号仪设置,没用过,不知道这样对不。我用不同的窗函数结果差别很大,我想改采样点数但是只能是4096、1024等

4、我在后面还加了一个四阶的巴特沃斯低通滤波器,3db带宽12.5k,但是发现过了滤波器后噪低又被太高了,无奈。

下图是过了滤波器的噪低,和刚刚的测试情况一样。

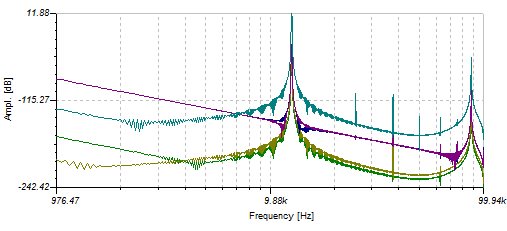

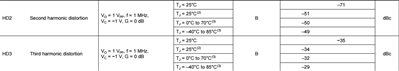

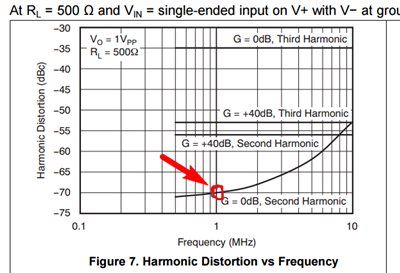

1.我尝试了VCA810这个器件的输出频谱仿真分析,发现通过其获得的频谱表现与手册给出的数据还是有差异的。

比如VO_PP=1V,负载为500,输入1M的情况下,二次谐波跟手册还是一致的,无论选用什么窗口,数据关系是一致的。

但是其后面的三次谐波与手册会有些差异,按照手册其三次谐波的还是很大的,比如在1M, Vopp=1V,GAIN=0的时候,其二次谐波为-70DB,,三次谐波的话会有-35db,其实这些值还是不够小。

所以我建议你参考手册PAGE12给出的谐波特性来对比实际电路会比较靠谱。

至于说窗函数,窗函数会改变频域波形,让频谱看上去不一样的,但是对于谐波分析来讲,其获得的相对幅度值应该是一致的,只是外观上看着有点不一样。

采样点数的话,越大其分析的分辨率越小,理论上低噪声会更小,这个好像是叫做处理增益。

在TINA里头其选择的电路最大只有4096,如果你想获得更加精确的频谱,可以尝试把扫描带宽缩窄,那么对应的分辨率就会上来。

至于说噪底很大,其实需要与谐波分开来看。

这个需要你一级一级的去测量,看下输出的噪声是否有超出理论值很多,必要时可以对每一级输出做带宽限制,看下主要的噪声源来自与那里。

谐波的话,第一级输出的谐波抑制是比较差的,建议你应当尽量控制这一级的幅度,谐波就是来自与非线性的放大,通过控制增益和幅度对于谐波的抑制应该会有效的。

好的,谢谢你的回答。前几天出差刚刚回来,我在看看!