VCA810达到输出摆幅限制前失真

时间:10-02

整理:3721RD

点击:

在使用VCA810时,输出没有达到手册上的输出摆幅现在就削顶失真了,后来用TINA仿真了一下,发现情况是一样的。不知道是什么原因?求解。

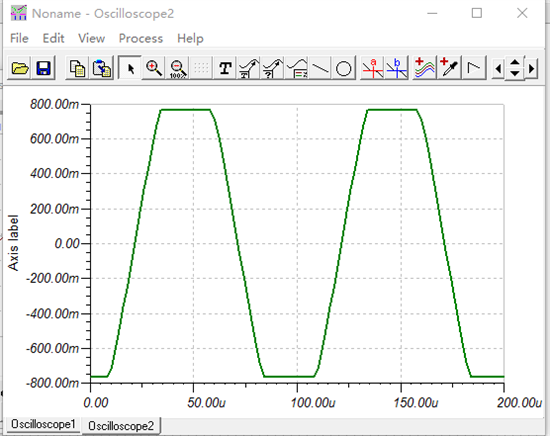

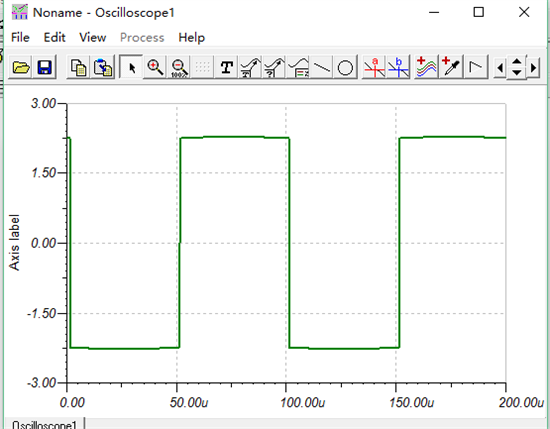

仿真的波形:

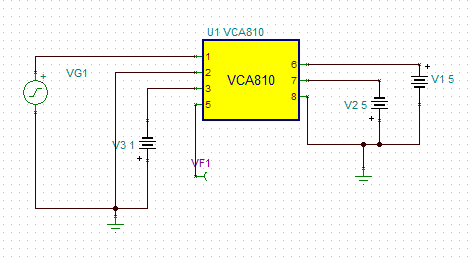

电路:

这个是从官网下载的Spice模型,同相输入,2、8脚接地,3脚负压控制端。

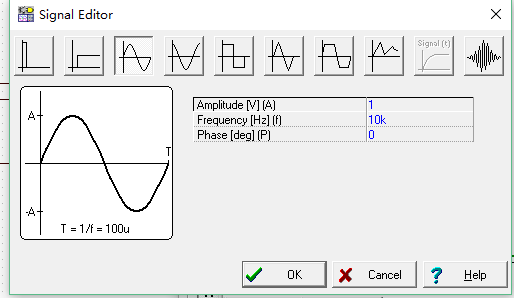

输入信号:

幅值1V,频率10K的正弦波

输出:

我的控制电压是-1V,这时不应该失真的啊,这是怎么回事呢?

顶一个

在仿真时,把控制电压由-1V改成-3V试一下

把VC改成了-3V,输出是这样的,应该是摆幅限制失真了

用TINA仿真了下确实是这样的,输出最大大概在0.8V附近,降低输入信号范围,大约在0.7V以下,G=1时输出跟随。

虽然符合它的输入共模电压范围,但输出为什么会削顶还需再确认下。

你好,首先谢谢你的认真回答!

我是先制作的电路,发现输出在很小就会削顶,后来,用TINA仿真了一下,发现情况竟然一样,佩服TINA的仿真,太真了,哈哈。

之后仿真乱搞一通(加负载,进行输入信号阻抗匹配等,不知道在仿真里面阻抗匹配会不会有影响?),仿真还是那样。但是,我重新测试了电路,发现情况竟然变好了,很是奇怪,我什么都没改。

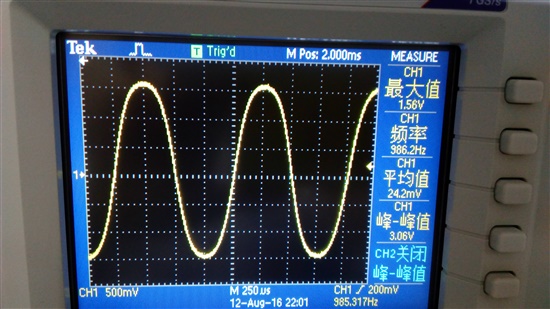

VCA810 3Vp-p的输出如下,波形有点‘胖’,没有出现削顶。