运放的共模抑制比与电源抑制比关系

时间:10-02

整理:3721RD

点击:

共模抑制比高的运放,是不是相对来说 电源抑制比就比较高呢?

共模抑制比 如果不是接成差分形式的话,是不是这个参数就不用考虑呢?

应该这两个参数没有啥对应关系.

运放是两路输入端的, 所以最终必然是差分输入, 还是存在共模抑制比

是不是共模抑制比是相对于运放的输入端来说的呢?而电源抑制比是相对于运放的内部来说的?

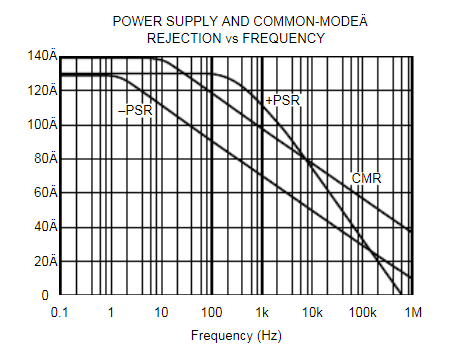

两个参数在运放的选型上都是很重要的,比如根据它们的定义可以看到表征输入共模电压和电源电压的变化对于输入VOS的影响:

选型的时候,它们之间没有直接的联系,特别在进行微弱信号放大的时候这两个越大越好。

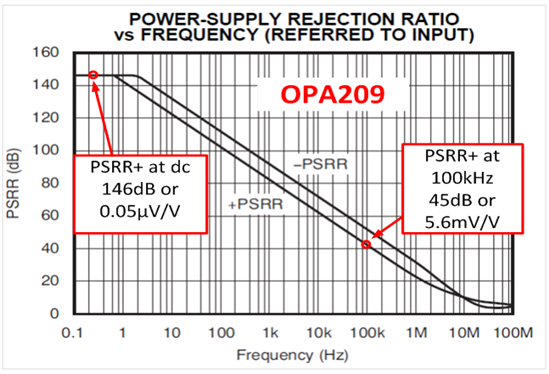

还有一点需要注意就是这两个参数并不是一个常数,而是一个与信号或(纹波)噪声频率有直接关系的变化量。

OPA277

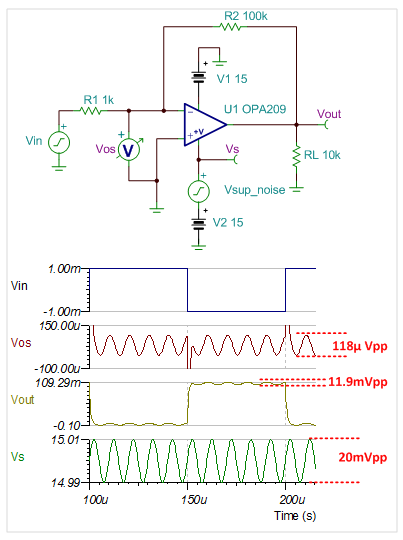

这个是做的一个仿真。

终于知道怎么样仿真电源的PSSR了 原来是在直流电源上面再叠加一个交流信号