芯片之ESD

时间:10-02

整理:3721RD

点击:

今天学习了TI有关“运算放大器:静电放电 (ESD)”的培训教程。

其实在实际应用中除非芯片资料特别提醒需要防护ESD,一般都不会去考虑ESD,都认为芯片静电防护等级>3KV。

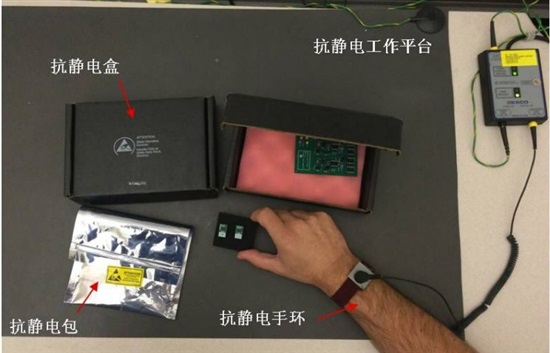

在实验室一般都会配备防静电手环,工作台铺设防静电垫。购买的芯片有的有防静电包装,有的没有。

资料显示:

在半导体器件最初的生产过程中,芯片的 ESD 防护性能(参数)就已经确定了。首先,大量的芯片样片经过自动化测试。一般来说,芯片数据手册上的大部分参数都是在这个自动化测试中,测量出来的。然后,一个专门的 ESD 测试系统对器件进行 ESD 脉冲仿真测试。这个 ESD 脉冲的参数是由测试硬件控制的。比如,我们可以选择脉冲的幅度和 ESD 模型。简要来说,ESD 模型通过设置电容,电感和 ESD 电流等参数来模拟现实中的 ESD 现象。在测试过程中,ESD脉冲加到芯片的多个引脚和引脚的不同组合上。同样的,我们采用不同级别的 ESD 脉冲对芯片进行测试,比如 1kV,2kV,3kV 等。

那么能否给出各类放大器的ESD等级列表,方便工程师使用。可以按不同类的放大器,给出它的静电电压范围,防静电等级,而且对于其它器件,如电压参考,ADC,MCU,DSP等也可以给出参考防静电等级。需要特需防护的产品或一类器件,可特别指出,减小应用中的问题。

期待TI的工程师们能有统计数据。

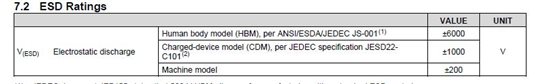

多数运放的数据手册中都给出了ESD的等级,包括HBM和CDM,Machine model三种模型的值都会给出

比如下图是OPA2836的ESD信息

对于ESD敏感器件,器件手册中也会有标注的,不过一般不太明显,你需要注意一下