Riso 与 RL分不清,它们是什么关系,我搞不懂!求助

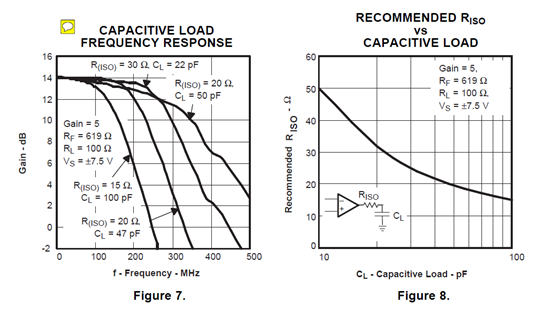

在看运放数据手册时,遇到两个电阻Riso(隔离电阻)与负载电阻RL,在看运放稳定性资料的时候,得知Riso与运放的稳定性有关,而RL表示了运放的驱动能力,但是我不懂的地方是:这两个电阻都是接在了运放的输出端呀,它们两个都在电路的同一个位置,那我怎么区分它是隔离电阻还是负载电阻?在看上图中,我看到,运放容性负载的驱动能力是在负载阻抗RL=100欧的条件下测的的,可见,RL与Riso根本就不在一个位置上!这是什么情况?

你要是有个实例,则好讲了。Riso一般是隔离容性负载的

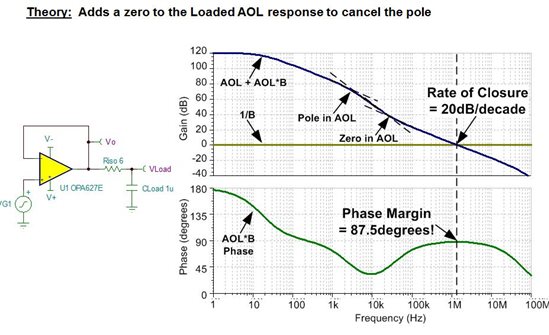

RL指的是负载,Riso则是用来改善运放稳定性的,其原理是增加一个零点来消除极点,如下图:

你好,在输出端存在一个开环阻抗Ro,存在于反馈环路内的。在驱动容性负载的时候,Ro与CL就会形成开环增益上的一个极点,这个时候在Ro和CL之间插入一个RISO,引入了一个由Riso*CL确定的零点,同时把Ro*CL在开环增益上形成的一个极点变成了由(Ro+Riso)*CL确定的另外一个极点。最终在以到达0dB前把开环增益曲线修正过来,实现-20db的滚降速度。

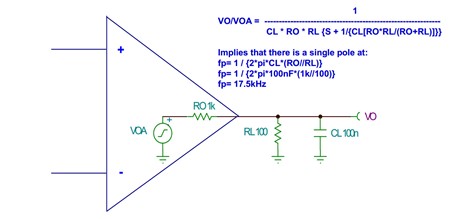

负载电阻RL是处在反馈环路外,与容许负载电气上并联在输出端的。它同样会影响到极点的位置,如下图:

根据戴维南定律,其最终与CL形成极点的电阻应该为RO//RL,这样会把运放的第二个极点(一般)的位置往后推,如果RL》10RO的话,负载电阻对于稳定性的影响可以忽略。

我们可以根据上面的图比较容易辨识出RL和RISO,RISO就是串在RO和RL之间的一个能改善系统稳定性的隔离电阻,而RL是与CL并联的一般对系统稳定性没有影响的负载电阻。

希望上面的解释对你理清RISO和RL有帮助,如有不同意见,欢迎回帖。

你好,下面是几个问题(针对上图所示的电路而言):

1.如果我想要加个隔离电阻Riso,加在Ro与RL之间,还是RL与CL之间?我的观点是加在RO与RL之间

2.倘若将Riso=50欧的隔离电阻加在RO与RL之间,对运算放大器而言,它的负载电阻仅是是RL呢,还是(RL+Riso)呀?我的观点是:运放的负载电阻应该是RL+Riso,即150欧,我的观点对不对?对运放负载的概念我还有点模糊,求助

你好,

1.如果我想要加个隔离电阻Riso,加在Ro与RL之间,还是RL与CL之间?我的观点是加在RO与RL之间

是的,Riso就是把运放的输出端(就是Ro右端,Ro是个等效值)与负载(RL & CL,在这就是两端并联在一起)隔离开,重构零极点。

2.倘若将Riso=50欧的隔离电阻加在RO与RL之间??对运算放大器而言,它的负载电阻仅是是RL呢,还是(RL+Riso)呀?我的观点是:运放的负载电阻应该是RL+Riso,即150欧,我的观点对不对?对运放负载的概念我还有点模糊,求助

对的,增加的这个隔离电阻Riso对于运放来说都是负载,会对输出精度有一些影响(反馈点会有改变)。

学习了,谢谢