运放参数的详细解释和分析-part11输入阻抗和输入电容

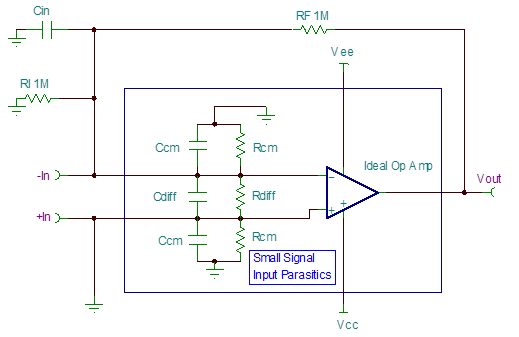

下图形象的说明了运放的输入端阻抗的特性。主要有两个参数,输入阻抗和输入电容。对于电压反馈型运入,输入阻抗主要由输入级的决定,一般BJT输入级的运放。的共模输入阻抗会大于40MΩ。差模输入阻抗大于200GΩ。对于JFET和CMOS输入级的运放,输入阻抗要大的多。这个阻抗通常表现为电阻性。作为常识被我们所熟知。

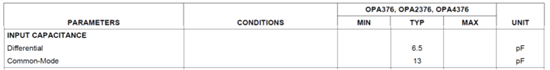

更值得我们多加关注的是运放的输入电容。这个参数通常在datasheet的表格中所列出,但常被忽视。运放的输入电容,通常分为共模输入电容Ccm和差模输入电容Cdiff。如下面是OPA376的datasheet中列出的输入电容。

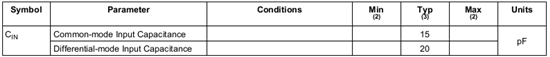

对于有EMI抑制特性的运放,如LMV832,它的输入电容会被设计的正大的些。下面是带EMI抑制功能的LMV832的输入电容值。

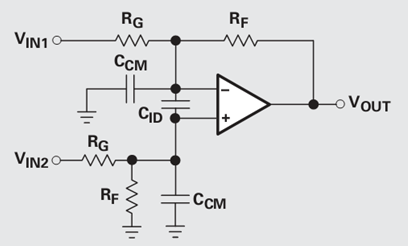

运放的输入共模电容Ccm 和差模电容 Cdiff会形成运放的输入电容 Cin。在许多应用中,运算放大器的输入电容都不会造成问题。但在某些应用中会引起放大电路的不稳定。尤其是反向输入端的电容,是放大电路不稳定的几大罪魁祸首之一。如下图所示是运放在有输入电容的影响下的模型。

这个反向输入端的电容会在运放的环路增益中引入一个极点。正是这个极点的存在,在某些条件下,可能会引起放大电路的不稳定。

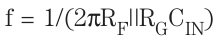

运放输入电容引入的极点如下式。即使这个极点0-dB交截越频率之内,而是非常靠近0-dB交越频率,它也有可能引起问题。在这个极点的频率点上,相位会有45度的相位延迟,它很可能减少放大电路的相位裕度。如放大电路的0-dB交截越频率是2MHz。在2MHz处的相位裕度是89°。 如果这个极点的频率点也在2MHz处,它将使相位裕度减少45°。而变为φ = 89° – 45° = 44°。 44度的相位裕度就显得的不够了。

通常放大电路的输入电容不只由运放的输入电容组成,还包括布线引起的杂散电容和引脚电容。应尽量避免运算放大器反相输入端存在外部杂散电容,尤其是在高速应用中。反相输入周围区域应去除接地层,从而最大程度地减小PC板杂散电容,此外,该引脚的所有连接都应尽量短。

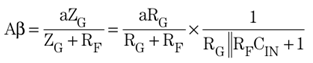

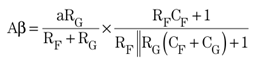

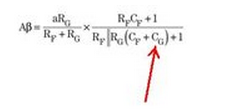

在一些应用,常会加入反馈电容来增加放大电路的稳定,加入反馈电容后的电路的环路增益为,可见反馈补偿电容给环路增益中引入了一个零点。

关于运放电路稳定性,可以参阅Tim Green的系列文章。

Operational Amplifier Stability。

请问加反馈电容后的公式里面的Cg是不是就是运放的输入电容Cin?

这里,应该是反指运放的输入电容和输入端的寄生电容。

加入反馈电容的好处,就是可以抵消由于运放输入电容和输入端的寄生电容引起的环路不稳定。

设运放的输入电容为5pF,工作在MHz级时,对地阻抗为1/2piFC = 1/ (2*3.14* (10^6) *5* (10^ -12) = (10^5)/3.14 = 32k 欧,这点阻抗在传感器放大领域怎么够啊。