运放增益小于1有什么影响,两级运放级联问题

TI专家,

有两个问题想请教,

1)一般运放的增益小于1了话,会对电路产生什么影响,是不是一般不会这么使用。

2)目前想用两级运放搭一个放大倍数40左右的电路,输入信号最大75mv ,直流信号,在选用运放时,除了需要选用低VOS的运放,两级运放,哪一级的放大倍数大比较好,如何处理能够减少噪声的影响?

增益小于1,没啥不妥。缓冲放大器有些就是用1增益的。

关于75mV放大,用低失调运放即可。从我个人经验看,两者设置为前低后高即可。两者差异不建议太大。

你好,关于你第一个问题,当比例运放电路中设置增益小于1(衰减器)是应该要注意两点:

1.首先是用于反馈电阻非常大的值时。这有几方面:更多的系统噪音,更大的失调电压和稳定性。大的反馈电阻,随着放大器的输入和杂散电容,引入在放大器的反馈响应的一个极点,这会导致额外的相移,从而降低了放大器的相位裕度,并且可能导致不稳定性。

2.一个更重要的考虑是噪声增益。噪声增益。例如,如果一个反相放大器具有-0.5的信号增益,它仍具有1.5的噪声增益。

你好,根据你的需求,输入为75mV, 增益设置为40,那么输出就应该为3V,当你选用VOS=10uV,输出端也就是0.4mV,这样的选型要求看起来还是比较容易的。

对于噪声的考虑,可以选用输入电压(电流)噪声密度较小的运放,比例网络的电阻不能选得太大(热噪声)以及供电电源和布线的考虑等等。

谢谢 Andy Tan解答,有一个不理解的地方就是为什么-0.5的信号增益仍具有1.5的噪声增益呢

那级联的两个运放的增益我如何匹配比较好呢。

我在用TINA仿真时,还发现了一个奇怪的问题,仿真图如下

输入75mV, 我用两级运放一共放大40倍,第一级8倍,第二级5倍

很奇怪的问题是,当我反馈电阻取得比较大时,较为准确,2.98V(理论值为3V)

而反馈电阻小时,差的比较大,2.89V,

小电阻的噪声不是小么,为什么仿真时会出现这种问题呢

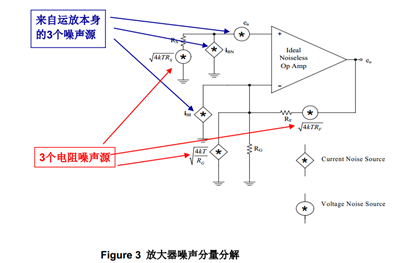

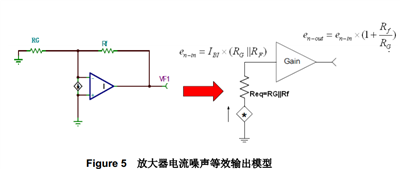

我知道的比例运放里面,输出噪声主要来源于电阻噪声和运放本身的电压和电流噪声,而来自于正端输入的电压噪声, 其折合到输出端的增益是等于噪声增益, 也就是1+RF/RG

运放自己的负端有一项是电流噪声,可以建立下边的模型,其噪声增益也为1+RF/RG。

所以无论是同向比例运放还是反向比例运放,其噪声增益都应该为1+RF/RG。

麻烦提供下你的仿真原文件