请教关于运放的输出保护问题

选择DAC8563和OPA2227,设计一个信号源,输出端所带的负载阻抗假设在1K欧~10M欧范围内,要求输出信号的精度小于1%,如附件所示。对于输出端有可能和GND短接的情况下,是否需要添加短路保护电路,如何设计比较好?请高手指点一下,谢谢。

一般OP运放在输出端会有过流保护机制的.

你也可以通过利用JFET最大有限IDSS来限制运放输出最大输出电流在IDSS.

也就是说对于OP运放来说,输出端短路是不会造成损坏,可以不用特意加保护电路了,可以这样理解吗?

要视具体情况而定吧。。。

不是定死的

那针对利用OPA2227来作为电压型信号源的输出这种情况,运放输出端只是添加滤波电容,而不增加其他元件,这样在出现输出端和地短接的情况下,是否会对损坏OPA2227?

基本上每一款的运放,datasheet中都会给出输出短路电流Isc这个参数,也就是输出短路保护机制,对于OPA2227同样,给出的输出短路电流的大小为+-45mA, 并且在“ABSOLUTE MAXIMUM RATINGS”里也给出Output Short-Circuit(2) .............................................................. Continuous(note2:Short-circuit to ground, one amplifier per package.),这说明输出短路可能并不会对器件造成损坏,但note2给出的条件指的是如果是多通道的运放产品,只允许其中的一个channel发生短路现象。OPA2227就是2个通道的,如果2个通道同时发生短路,则有可能对器件造成损坏。

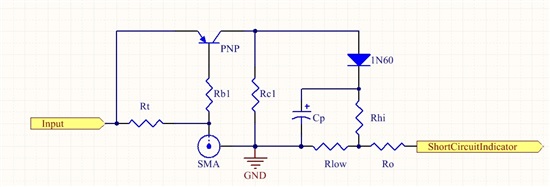

给楼主推荐一个简易的短路检测电路,如下图,画的可能不是很好请见谅:

Input是楼主放大器的输出,SMA是接负载的端口,ShortCircuitIndicator是短路指示端。(以后简称SCI)

楼主可以通过调节Rt的大小来调节输出电流限流的大小。

当流过Rt的电流乘以Rt的阻值,大于三极管PN结的导通电压时,三极管开始导通,随后SCI的电平由低变高。

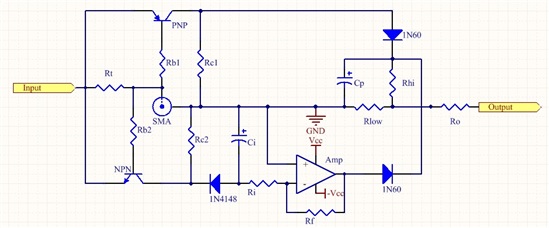

当然这个电路图只限输出电压为正的情况。如果输出电压存在负电压的情况,那么电路略微复杂一些。贴上来供楼主参考:

Hi Vio,

请问你使用的绘图软件是已获得注册的正版软件吗?看起来像是Autium Designer?能否给我分享一下子

Carter Liu

是Altium Designer,在ESD上可以下载:

http://esd.itg.ti.com/

根据More Info里面的说明,给Teresa.M.Posten@ti.com发一封邮件,申请Alitum Live帐号密码。她帮你注册好了之后,你就可以下载Altium Designer的安装器,链接如下:

https://sps06.itg.ti.com/sites/KMS/crossdivteams/altium/docs/InstallerFromAltium/AD/AltiumInstaller.exe

下载之后,一步一步的进行,在出来的注册页面上输入您的Altium Live帐号与密码即可完成安装。

用正版的Altium Designer略烦,每次打开之后都要重新输入一遍自己的Altium Live的ID与密码。

供参考。

非常感谢!困扰我很久的问题终于有答案了

太好了,我也来申请一下账号密码,感谢carter和Vio。

Kailyn Chen & Carter Liu 你好,你们两个都是我在deyisupport上非常专业热心的专家,以后有问题还望多多指教,互相交流共同进步