运放的差模增益的检测电路

这个电路该如何分析?

等效电路是什么样子?

公式是怎么推倒出来的?

还有没有其它的办法求开环增益?

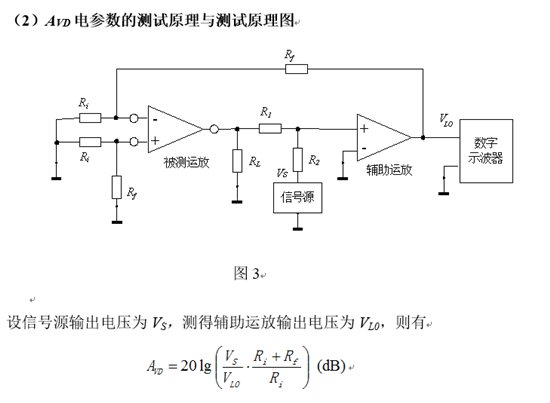

有关开环增益的测试以楼主所给的图为例,Vs要分两次提供,分别为Vs1和Vs2,设被测运放的输出端电压为Vo,则有Vo1=-Vs1, Vo2=-Vs2(根据运放的虚地概念)。得到两式:Vlo1=(1+Rf/Ri)*(Vos+Ib*Ri)-(1+Rf/Ri)*(Vs1/Avd)和Vlo2=(1+Rf/Ri)*(Vos+Ib*Ri)-(1+Rf/Ri)*(Vs2/Avd);两式相减得到:Vlo1-Vlo2=(1+Rf/Ri)*(Vs2/Avd)-(1+Rf/Ri)*(Vs1/Avd)=(1+Rf/Ri)*[(Vs2-Vs1)/Avd],整理就可以得到楼主给出的公式了,其中Vs=Vs2-Vs1, Vlo=Vlo1-Vlo2.

附件中采用的是false summing junction的方式来测试Aol, 你参考一下,如果有问题欢迎提问。谢谢!

我的数学学的很差,算起来很吃力不懂这个,麻烦再解释下。 Vo1=-Vs1, Vo2=-Vs2(根据运放的虚地概念) 我算的是Vo1=-R1/R2*Vs1, Vo2=-R1/R2*Vs2Andrew Wu

有关开环增益的测试以楼主所给的图为例,Vs要分两次提供,分别为Vs1和Vs2,设被测运放的输出端电压为Vo,则有Vo1=-Vs1, Vo2=-Vs2(根据运放的虚地概念)。得到两式:Vlo1=(1+Rf/Ri)*(Vos+Ib*Ri)-(1+Rf/Ri)*(Vs1/Avd)和Vlo2=(1+Rf/Ri)*(Vos+Ib*Ri)-(1+Rf/Ri)*(Vs2/Avd);两式相减得到:Vlo1-Vlo2=(1+Rf/Ri)*(Vs2/Avd)-(1+Rf/Ri)*(Vs1/Avd)=(1+Rf/Ri)*[(Vs2-Vs1)/Avd],整理就可以得到楼主给出的公式了,其中Vs=Vs2-Vs1, Vlo=Vlo1-Vlo2.

Vlo1=(1+Rf/Ri)*(Vos+Ib*Ri)-(1+Rf/Ri)*(Vs1/Avd)和Vlo2=(1+Rf/Ri)*(Vos+Ib*Ri)-(1+Rf/Ri)*(Vs2/Avd) 这个更是不懂。后面的那个运放输入跟输出到底是什么关系,它工作在开环还是闭环状态,您画的有没有等效电路,简化下,麻烦了!

感觉后面的那个运放好像一个过零比较器,工作在开环状态,为什么会有浮地?

我又重新算了一下发现公式成立的前提是前面一个运放要工作在开环状态下,后面一个必须要工作在闭环状态下才成立。但是这个开环闭环要怎么判断?