OPA1632与THS4150的问题

是用opa1632时,按照典型应用电路接的,但是,对于接法不是很理解,如opa1632手册 Figure11所示,对于其中的R5、R6、C3进行滤波这个说法,截止频率怎么计算? 还有,为什么要把R5、R6放到反馈电阻的里面,而C1、C2却放在直接接到运放的输出引脚上? 这样做有什么好处?

在THS4150的手册中,如Figure35所示,C2、R3的作用是什么?为什么要接这两个电阻和电容?这种用法与上述OPA1632 的用法有区别吗?抗混叠的截止频率是由C2、R3决定还是由C3、R4、R(t)决定?

在THS4150的手册中,如Figure41所示,这样做的仪表放大器,怎么去设置 类似单端输出仪表放大器那种的REF端?

对于opa1632,R5和C1反馈为AC反馈回路,R5和C1形成开环增益上的一个零点,进行相位补偿,使运放工作趋于稳定。同理C2和R6也是同样作用。

THS4150中,C2用来滤除差模干扰,C1构成AC反馈回路,和R3构成开环增益上的零点进行相位补偿,和OPA1632用法相同。C3和R4构成低通滤波,滤除共模干扰。

THS4150 datasheet中图41是采用了其全差分特性,和前面输入级组成全差分仪表放大器,其共模偏置可以通过Vcom管脚在输出级设置共模偏置电压。

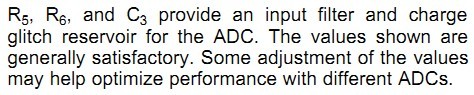

您这个说法不是很清楚。既然是抗混叠滤波,就应该有确定的截止频率。一般设置是:Fs/2.56,(Fs为AD的采样频率),这个用法经过这段时间的查阅资料,应该是在全差动放大器上做的“无限增益型低通滤波器”。

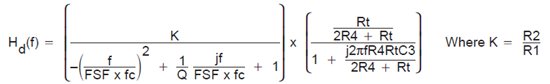

对于THS4150手册中公式:

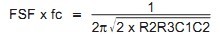

;其中,fc为截止频率,FSF为频率缩放因子,那么这个频率缩放因子是个什么概念?计算截止频率fc时,FSF怎么参与计算?

;其中,fc为截止频率,FSF为频率缩放因子,那么这个频率缩放因子是个什么概念?计算截止频率fc时,FSF怎么参与计算?

使运放趋于稳定是对的,因为若按平常的用法,没有R5、R6,则会由于后面有个容性负载C3导致运放自激震荡,加入R5、R6有提高稳定度,防止自激震荡的作用。

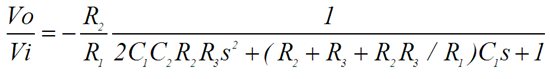

然手册中说:

特别是提供一个输入滤波器这个说法,仍没有说清楚滤波器截止频率的问题,还有,这个值是大体上令人满意的,少许的改变能提高差分ADC的性能,请问,我不知道该截止频率怎么计算,怎么改变?难道只能用multisin去仿真着试吗?

特别是提供一个输入滤波器这个说法,仍没有说清楚滤波器截止频率的问题,还有,这个值是大体上令人满意的,少许的改变能提高差分ADC的性能,请问,我不知道该截止频率怎么计算,怎么改变?难道只能用multisin去仿真着试吗?

仪表放大器的REF端用来接电路的共模电压,也可以用来调整电路的失调电压,如附件图示。我们用这种方法来调整电路的零点

但是在THS4150 datasheet中图41所示的全差分仪表放大器,微调Vcom端电压,能用来调整电路的零点吗? 如若不能,我需要怎么改才可以?

单端等效模型如下图

从Vi到Vo的传输函数H1(s)

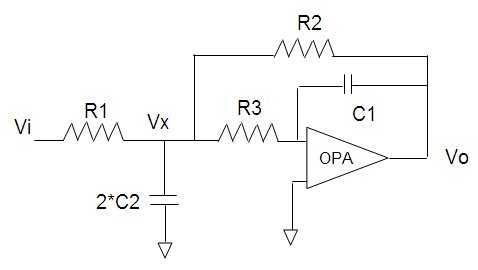

电路总的传输函数如手册16页所示

H1(s)就是Hd(f)第一个括号里的部分,其中把FSF*fc看成一个整体即可,或者说,H1(s)的两个根,他们的积就是FSF*fc。

不能,VCOM对两个差分段都有效,输入带进来的DC offset,用VCOM干不掉。如果要改,就在前级把零点调好再进来。

另,最近做所谓“宽带直流放大器”的人不少,用VCA的,THS的,都有。个人认为,试图在模拟端完全干掉DC offset不现实,也没必要。可能你调三天三夜,调出来的结果,还不如我在数字域写一个简单的DCOC算法来得有效。再者,靠这种所谓“运放调零”调出来的“零点”,过不了高低温,你就算是在常温下调出来了,进了温箱一样挂。所以,建议是,把DCOC交给DSP/FPGA,模拟域别搞得太大就行。

还是那个说法,如果我的AD是±5V的量化范围,在模拟区有+10mV的offset,如果不是在模拟区修正掉,那么最终AD的量化范围就变为-4990mV ~ +5010mV的量化范围,我可以在FPGA中减去10mV对应得码值来修正零点,但是客户会说:你们的产品怎么测不出来-4995mV的电压?这是一个致命的缺陷,直接就是测不准的问题,精度再高又有什么用!

音频领域的AD,比如PCM4220,可以开启高通滤波器,自动消除offset,然而没有发现它存在上述的问题,再次请问:音频AD的这种自动消除offset的机制是什么?怎么做到既消除offset,又不影响测量范围的?如果是在DSP上实现这种机制,该去怎么做呢?

看应用了,如果是用在音频领域,则运放肯定要选低失调的;如果用在高速,或说通信领域,运放就没必要那么追求低失调的目标。如果真的把直流失调校准到非常低的水平,用那种变阻器调零电阻的方式,多半是不行。你如果感兴趣,可以找找DCOC的资料,估计是用一个辅助运放和大电容,结合软件算法一起做,其中辅助运放和大电容用来做DCoffset的储存和反馈回主运放输入端。

音频的频率范围是2K~20K,如果DSP里处理的信号也在这个范围,或者再宽一点,比如1.5K~40K,那么可以设计一个很陡峭的高通滤波器,在直流和几十Hz的地方有很高抑制,在信号频带内平坦,不影响信号质量。另外,即使DC offset会把音频信号向上或者向下“搬移”一部分,一般也不会使信号碰到ADC的full scale,所以就没问题。