关于运算放大器芯片的压摆率设计问题

时间:10-02

整理:3721RD

点击:

本人不是做芯片设计的,所以请问懂运算放大器芯片设计的工程师朋友,运放的正向压摆率(SR+)和负向压摆率(SR-)在通常情况下,是很接近的,然而有些运放却不是,如TLV2401系列芯片,压摆率曲线如下图所示

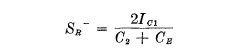

我的问题是:SR+和SR-可以任意设计吗?比如SR+ = 10*SR-。如果可以的话,有什么相关的书籍或资料可以参考吗?我看过关于集成运放Spice宏模型的论文,里面在做宏模型时,提到了SR+和SR-的计算公式,如下图所示

从公式来看,SR+和SR-是可以灵活设计的。

楼主您好,感谢您的经验分享。

影响SR因素的主要原因是内部的补偿电容,补偿电容的目的是让运放拥有稳定的单位增益。 未加补偿电容的运放SR是由内部分布的电容决定的,如这里的C2,C1。 未加补偿电容的运放比加的运放有更快的SR。SR+和SR-的大小我们一般尽量做到匹配,不一样的话对于单纯对于SR来说应该意义不大。 您提供的图中应该仅仅是一个典型,这里连接到C2上的电流是C1上的两倍,所以是2*IC1。 SR 的设计不是任意的,和外部补偿一样,总是需要牺牲的。 楼主如果有更多的观点和信息也欢迎和我们分享。

正向和反向压摆率不同的原因,是输出级结构不同造成的。运放的第一级和中间级之后,输出级上管和下管的实现结构有很多种方式。