运放的位数

我以前我只听说过模数或者数模芯片有多少位,但在TI的资料中我看到有运放是12位的,请问这是怎么来的?

最好把资料放上来,大家一起参考一下。

我猜测,资料上的意思是说运放的噪声和offset指标可以满足驱动一个12bit ADC的需求,所以把这个运放叫做“12位运放”。比如一个3.3V参考的12位ADC,它的LSB是3.3/4096~=0.8mV。一般单运放的输出总噪声做到小于1/2LSB=400uV很轻松,如果运放的最大offset指标也满足小于400uV,在满足带宽的条件下,这样的运放就可以驱动12位ADC。

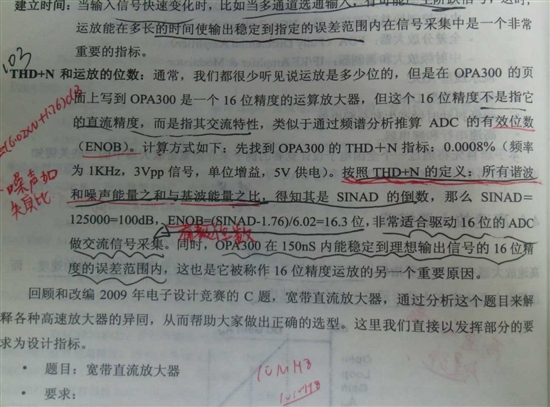

你好,这是我从书上拍下来的图片,我看了后还是不太理解运放的位数是怎么回事?

1. 150ns能稳定到理想输出,说明带宽/速度没问题。

2. THD+N表示总谐波失真加噪声是0.0008%@ 1KHz,3Vpp输入,意思是说,当输入信号是1KHz的时候,运放对信号的失真(谐波+噪声)是0.0008%,则可以达到的SINAD就是1/0.0008%=125000,换算成对数就是100dB,然后换算成ENOB就是16.3位。另,OPA300手册第三页THD+N这个指标是0.003%,你那个资料上是不是写错了?

3. THD+N在低频时的确很好啊,但是到了高一点的频率,几百K或者上M,就会掉下来了。这个要看你想处理的频率了,如果处理的是100K的信号,就不能参考1K地方的THD+N了。

这里16位精度的运放是针对16位ADC来说的,意思是OPA300的交流误差不超过1/2LSB(16位ADC的分辨率),主要包括noise等一些交流参数。

ENOB就是16.3位是怎么算来的?

对于交流信号特性,ENOB=(SINAD-1.76)/6.02,SINAD=20log10(full-scale input/noise). 式中1.76 和6.02是以理想转换器量化噪声模型计算出来的,可以在网上搜一些相关资料翻阅一下。