关于OPA656两级放大的问题咨询

电路图见附件

第一级电流完成I-V变换,第二级电路对电压进行放大,两个运放的输出都接入采集系统,即实现不同量程,以满足不同动态范围信号的测量

输入电流信号的带宽在10M左右

两级运放直接直接连接电阻有没有问题?

需不需要电容隔离?

另外我去年使用的时候,有发现死锁的情况,即正负电源没有同时上电,芯片不能正常工作了。

hi zhidong,

看您的第二级更像是一个反相,您指的不同量程是不是ADC的N/P?如果是想单端转差分这种方法实不可取的,简单的可以直接用全差分运放。

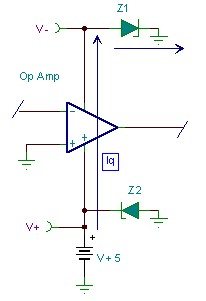

发生锁定的现象的确是因为正负电源没有同时上电造成的,因为电源的静态电流造成的,如果无法同时上电,建议加diode如下:

我的目的是这样的: 第一级运放实现IV转换后 直接进采集卡数字化,第二级运放的目的是对第一级运放的输出电压进行放大, 因为输入的I的动态范围未知,所以我想通过这种方式保证我想要的观测数据的全波形。即对于小脉冲信号,能够利用第二级运放获取较高 的动态范围,对于大脉冲信号,第一级直接输出,防止输出的饱和。 我不确定 第二级运放直接接上去 有没有影响? 我去年应用该电路时只有I-V变换电路,今年准备加上第二级运放

好的,谢谢!

请问二极管有和参数要求?其目的是什么?是防止静态电路流入运放吗?

是的。齐纳二极管的选择依据电源大小来决定。

通过简单的无负载下仿真来看并不需要隔离能完成基本的传输,但个人觉得这里是高速信号,从信号完整性角度来说并不建议直接采用'Y'形的接法。

根据您的功能描述看起来并不需要两路同时工作,何不直接加一般的开关或者SPDT模拟开关做控制。这样就能直接避开两路的‘干扰’。

死锁的问题已经算解决了。

其实我是希望两路同时工作的,因为输入信号中同时包含大脉冲和小脉冲。

第一级运放是完成I-V变换,然后直接输出。第二级是在将第一级输出再放大N倍。

如果只使用一级放大,就会出现小信号放大倍数不够,或者大脉冲测量饱和的情况。

您提到Y形的结构不合适,请问有其他方案吗?

如果是同时输出建议可以用1 to 2 的buffer 做fan-out,如果是在分支上做一对一隔离尽量缩短节点到隔离器的路径并做好阻抗匹配。

是同时输出。

不太理解,用1 to 2 的buffer 做fan-out?是什么意思 那是要重新选运放芯片了吗?

麻烦解释,因为板子已经做了,还没有发出去做印制板,非常着急 ,没有底

能否详细解释下,非常感谢

我这样的需求 ,选用656是不是有点浪费?

1 to 2 的buffer 指的是1进两出的switch 或隔离器,主要可以增加驱动和提高信号完整性。

但如果您已经做好了板子可以不必加,Y形输出虽然会对信号造成non-monotonic,即信号上升或者下降过程的‘肩膀’,但这个可以做好阻抗匹配来解决,

所以您的后面两个分支请注意阻抗匹配。具体信号完整性请注意测量。

另外两个分支的驱动都是由第一级I-V转换的AMP提供的,布线不宜过长,注意ADC处的衰减。

OPA656是比较优秀的跨阻放大器,不仅具有高的带宽,而且拥有较低的电流和电压噪声。比较便宜的您可以看看LMH6629等其它器件。

好的 非常感谢!

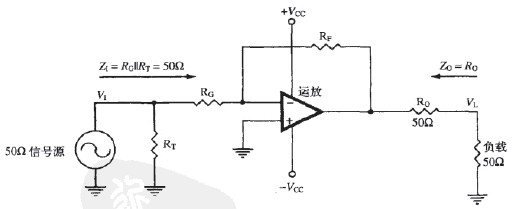

基于我附件中的电路图,请问,关于阻抗匹配,特别是第一级IV变换和第二级运放 连接 需要注意什么吗?

电阻值如果选择保证阻抗匹配?

当时选择OPA656 主要是看中其是单位增益稳定

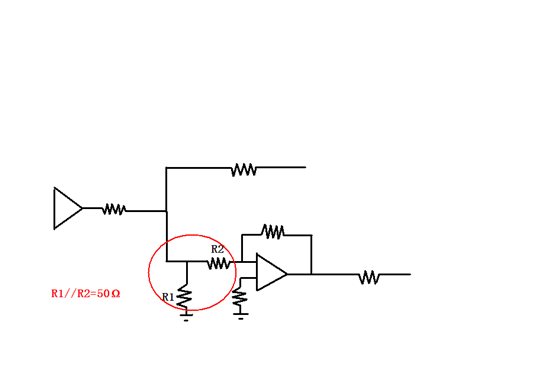

注意点应该在于第二级运放的输入端,需要加入一个如下图的接地电阻来进行匹配

能够用于I-V转换的跨阻放大器都需要满足单位增益稳定

是第二级输入阻抗 (即R1和R2并联的阻抗) 和第一级的输出阻抗 一致吗?

是的,例如下面的例子,也就是说如果您的第一级运放后面会接50Ω电阻做匹配(从分支点像前端看过去),后级的线路也要做好相应的匹配。阻抗匹配就让信号正整个通路过程中不会感到明显的阻抗变化,这样上升下降等特性都会较为平滑一致。