MFB高通滤波器multisim仿真会出现翘角现象

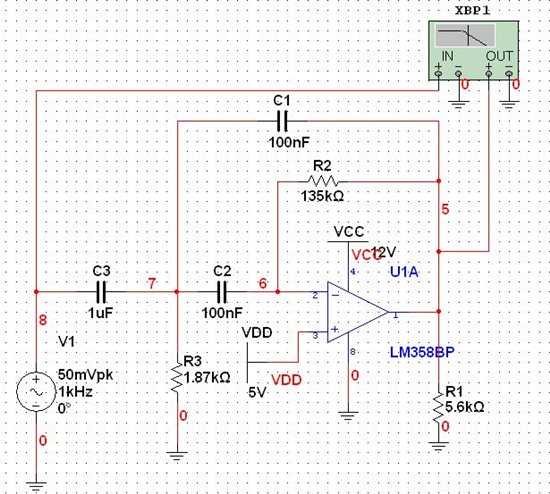

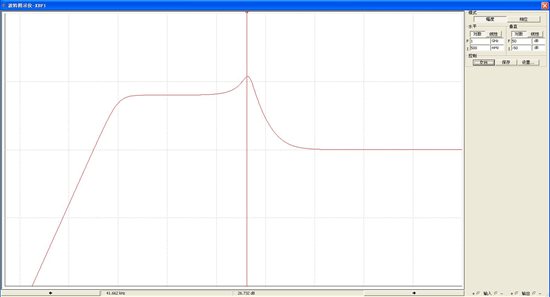

如上图所示:MFB高通滤波器,截止频率100Hz,用公式计算的参数,multisim仿真后发现大概在30kHz时会出现翘角现象(翘起有6db),且之后的频率有所衰减。这是为什么呢?

楼主你好!

类似问题之前有过很多讨论了。

1、因为滤波器设计软件是根据理想放大器的特性去设计的,也就是把理想传递函数变成电路形式而已,没有考虑运放的实际模型的影响。实际运放本身可以等效为一个二阶系统。

2、所以,就会出现上述AC传输曲线,如果使用理想放大器仿真,则不会。

那我要怎么去调试呢?

现在调试发现,该高通滤波器会出现低通截止的现象,大概在15kHz之后会逐渐衰减,这是为什么呢?改怎么调参数呢?

Zhejun,

你的系统有可能不稳定。你可输入一个方波信号看有没有振铃。如果振铃幅度大,说明系统稳定性不太好。

运放的输入管脚有个寄生电容。该电容跟反馈电阻等一起会造成信号相位的滞后,有可能造成稳定性问题。

建议在频域进行相位和增益的仿真,调整电阻值 或者调整 并在R2上的小电容的容值,通过仿真找到一个相位裕量比较大,又比较合理的元件值。

关于高频变窄,在你的另一个帖子里应该已经回复。

Best Regards

Frank Pan

楼主你好!

1、二阶高通不建议用MFB结构的,不管你用什么放大器,都会有一个谐振点。

2、建议采用sallen-key结构的,请楼主给出要求,相位线性?通带宽度,截止频率,阶数等等?我帮你重新设计。。

为什么不建议用MFB结构,谐振点是怎么算出来的?

zhenjun,

对你的MFB高通,用理想运放增益是由C1和C3的容抗比决定的,因在高频,电阻的值远大于电容的容抗,可以忽略。

对实际的运放,输出阻抗随频率增加而增加。如果考虑到运放的输出阻抗,MFB高频的增益应当把输出阻抗加到C1的容抗上。这样,就造成高频的增益增加。

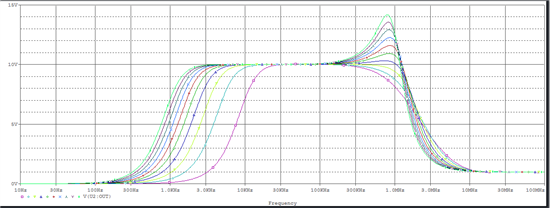

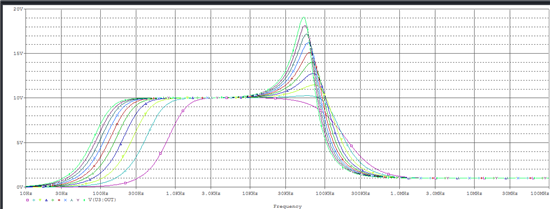

要让运放的输出阻抗降低,就要增加电容的容抗,即降低电容的容量。下图是采用不同的电容值,相同的比值的仿真结果:

因为电容值变了,需要同比例改变电阻的值,以使低频的截至频率不变(仿真时没改变)。

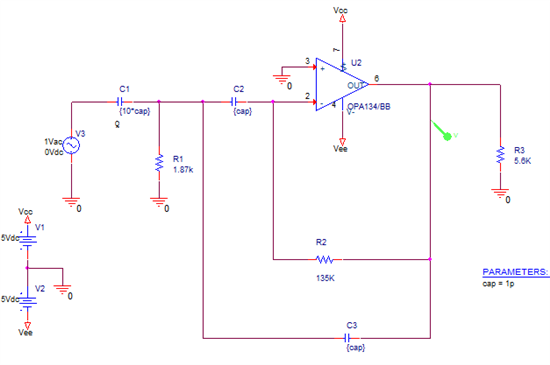

仿真用的电路图:

其中cap参数从1nF到10nF,以1nF递增。仿真结果图中,高频峰值最高的是10nF,最下面是1nF。

仿真使用的是高性能的OPA2134这类运放。从图中看出,高频的截至频率在1点几M,考虑到增益10倍,增益带宽积在十几M,跟芯片数据手册吻合。

如果要用LM358这类运放,输出阻抗较OPA2134大,但同时带宽较窄,需要调整电容的值。下图是用LM358,cap从10n到100nF,以10nF递增仿真的结果:

由于LM358带宽限制,在x10增益时,带宽只有100K。

需要指出的是,MFB高通滤波器在高频,对信号源呈现很低的阻抗,要求信号源有较强的驱动能力。

Best Regards

Frank Pan

高手,佩服!