ths7001级联问题

将两个ths7001级联 发现输出波形很不成样子 有时候是锯齿波 有时候是不成形的方波

我将两个断开

单测每一个7001时发现都可以单独工作 且我测后级7001的时候是以前级7001的输出电压值 作为信号发生器的输出电压值来为后级7001提供信号的

我考虑了可能是阻抗不能很好匹配

所以我在两级之间加了一个ths3001做的跟随器

测试时可以看到从第一级的输入到ths3001的输出都很完美 很和要求 但是一接上后面的7001

再测前级ths3001的输出 发现已经完全变形了

而最后的输出完全不成样子了

测试条件:

级联时输入0.1v的有效值 中频段 第一季设置为放大10倍 第二级设置为放大5倍 输出不成样子

单测条件

前级输入0.1v有效值 在ths3001输出0.9v有效值

后级输入1v有效值 输出为4.3v的有效值

单测都可以工作 级联后ths3001输出已经紊乱

请各位老师指教

谢谢

可以在第一级与第二级之间串一个20ohm左右的电阻试一下,省掉THS3001做跟随。

请问是直接加到后一级的3端口 是么

我加了29欧电阻 输出没波形 而且芯片发热厉害

你好。不建议使用THS3001电流反馈放大器作为跟随器使用,建议使用OP07之类的电压放大器作为跟随器。因为THS3001其负端的阻抗不大,且THS7001的PGA的输入的阻抗也不是很大,可以换电压放大器跟随调试一下。

你好 我想使用opa690

我按照datasheet上的反馈选择24欧电阻 但是实际测试发现电路直接自激

请问OPA690做跟随 有没有稳定的 不易自激的电路?

建议尝试在RF外加一个20p左右的电容,看一下测试结果;

此外个人觉得电压放大器作为跟随器是可以不用反馈电阻,但是这个开环增益才60db,你可以尝试着去掉这个反馈电阻试一下。

现在问题是690不自激了 但是输出直接接在下一级PGA输入级时 可以测得输出为-7V左右的有效值 直流电平 频率显示为500M

还有一个小细节 就是在接好没开电源时 可以看到示波器为20M的带宽 且不能被设置为全带宽

请老师指导这个问题该如何解决

谢谢

能不能上传PGA输出的波形,这样可能会更容易理解。如果可能的话,请给出整个电路的输入信号,690的输出和PGA的输出,可使用示波器的不同通道显示。

放大级太多了,这样很不好。前级的DC offset会直接被放大,并作为后级的输入信号继续被放大,造成的结果是系统输出端会有很大的DC误差。这种高速运放本身并没有对DC offset做特别的优化,所以像这种多级直流耦合的应用会很危险。建议把电路压缩到两级,第一级做放大,第二级做可编程放大和输出端驱动。

两个建议,一是做增益规划,看看每一级需要多少增益;二是做AC和瞬态仿真前先跑个DC工作点,看看DC offset是否能够接受。

问题已经解决 请问用什么方法能够很好的消除输出中的DC电压成分

或者说怎样减小前级的DC offset?

有相关的文档么

或者有什么易行的方法么

请老师指点

谢谢

1. 你的应用可以容忍这样的DC offset,那就没必要再做改动。

2. 试试级间交流耦合,就是级间用电阻挡一下直流,是否能够满足要求。

3. 级间还是交流耦合,在整个电路输出端用交流耦合和负载连接,再试一下。

我的应用不可以容忍这样的DC offset 所以我要设计电路来消除

由于我们做的题目要求必须直流耦合,而你说的交流耦合---用短租挡一下电流 我不是很懂 能详细解释一下么

还有你说的第三条我也不是很懂 有线路图说明么

最后问一个问题

有没有电压跟随器调零电路?

如果有可以提供一些相关资料么

我在网上搜不到相关资料

谢谢了

你整个电路的负载是什么?是个阻性负载还是个容性负载?或者说是两者的并联?

我的总体设计为

第一级采用OPA820将10mv的有效值放大10倍,得到100mv的有效值

第二级采用两个7001级联得到可控增益,从第二个7001输出的电压有效值应不小于5V的有效值

最后采用ths3091做功放以驱动一个50欧的负载 在负载上面要得到10V的有效值

我们的带宽为0-10M 整个题目为09年电子设计大赛的C题--宽带直流放大器

现在遇到的问题是从第一级7001输出的波形中 带有大约25-80mv(不大确定)的直流电压成分 以至于直接与后级7001进行耦合时后级7001不能正常工作 输出波形有较大失真

所以现在是想方法消除所谓的DC offset

我想用电压跟随调零电路实现 但是没有这方面资料 请问你可不可以提一些建议

其他方法也行

谢谢

之前做过用混合电路设计实现的DCOC,大致的想法是采样输出电压,并用比较器量化。然后在数字域做平均,把直流误差成分平均出来,然后把这部分误差通过电流源注入回运放的一个输入端,通过电流流过反馈电阻/输入电阻产生的压降来抵消DC offset。不过这个方法是集成到芯片内部的,用分立的元件搭成本太高,风险也大。你可以试试看用纯模拟的方法·是否可行,这种方法我之前见过,但是没有做过。大体上是运放的输出经过一个运放后,直流误差成分被储存在一个大电容上,同时这个大电容上的误差电压反馈回运放输入,从而抵消本级的DC offset。

另外如果条件允许,可以去IEEE Xplore上搜索一下DCOC(DC Offset Cancellation)方面的文章,或许对你有帮助。

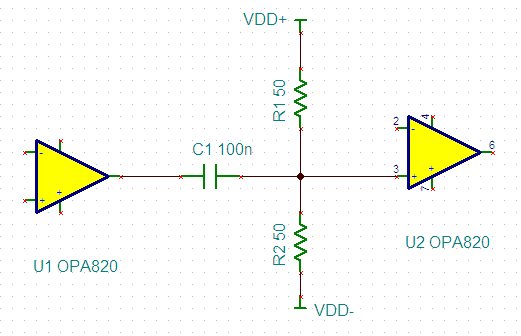

当然,最直接的办法是中间挡个电容,后端用电阻分压重建直流,如下图,你可以试试看。但是在高速应用中,不知道这种结构是否会恶化频率响应,可能还需要对容值和阻值做必要的调整。

调零电路我已经设计好了 而且调节效果也不错 但是有一个很棘手的问题让我很难解释

我前级opa820输出波形很好 而且可以调零实现uV级的失调电压

然而当将输出直接接下一级ths7001后发现:7001前级的运放输出同样完美 而且失调电压很小(也可以调整到uV级)

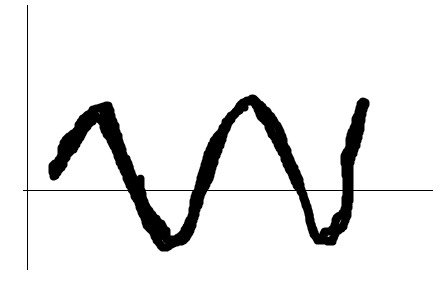

但是7001的PGA输出端的波形如图所示

波变得很粗

而且DC电压很大,我的测试时 输出有效值为1.2V 但是DC直流电压就有600多mv

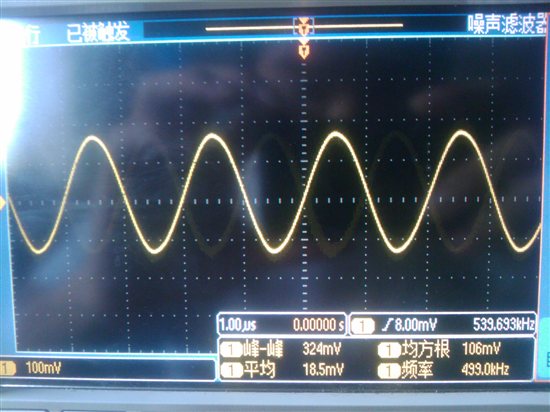

然而我用信号发生器测试ths7001

其输出很完美没有任何杂波 放大倍数也在预期之中

如图所示

后来我做了一些调整 将7001的3和4引脚之间的0欧电阻去掉 在7001输出端加了一个51欧电阻再测试

级联时的波形

单测7001波形一样完美 请问是什么内部因素在作怪

谢谢

整个电路发上来看一下,或许是调零电路的问题。另外,你应该是没有用到Pre Amp,能否试一下把调零电路的输出接到Pre Amp的输入上?就是把预放大器用起来。

下奶没问题了 可能是上午测试条件不好 或是电源有一点问题吧

现在的问题是后级7001发热

就是这个问题

www.deyisupport.com/.../11244.aspx

那个问题不知道为什么被删了。现在看来,DC offset的问题应该已经解决了,那你后级7001带多大负载?看看直流电源的电流档显示输出多少电流?

另外,现在最终版的电路是OPA820+THS7001+调零电路?820和7001各一片?

7001后面没带负载 空载直接用探头测试

你可以看一下我的电路图

方便讨论我在发一个帖子