FinFET(鳍型MOSFET)简介

1、半导体的工艺尺寸

在我们谈到半导体工艺尺寸的时候,通常对于下面的一串数字耳熟能详:3um、2um、1.5um、1um、0.8um、0.5um、0.35um、0.25um、0.18um、0.13um、90nm、65nm、45nm、32nm、22nm、14nm、10nm...有人说5nm是半导体工艺的极限尺寸,也有人说1nm是半导体工艺的极限尺寸;iPhone6s的 A9处理器更出现了三星14nm工艺和台积电16nm工艺二个版本、哪个版本更先进的激烈的争论。这里的工艺尺寸,通常是指集成电路的最小线宽,那么在集成电路的内部,最小的线宽是指哪一个几何尺寸呢?

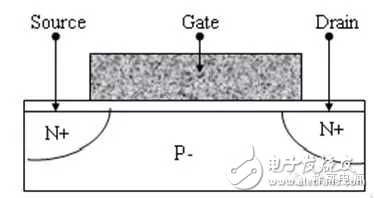

在集成电路的内部,最小的功能单元是平面横向导电的MOSFET,如下图所示,这个结构及其工作原理以前的文章介绍过:功率MOSFET的结构及特点,其由三个电极:G栅极、D漏极和S源极组成。

图1:平面横向导电MOSFET

灰色Gate栅极的宽度、也就是沟槽宽度或者线宽,通常所说的多少多少um、多少多少nm就是指的这个宽度,而不是每个晶胞单元的尺寸。

沟槽宽度的减小,可以带来如下的优点:

(1)沟槽宽度对应着D到S极的距离,沟槽宽度减小,载流子流动跨越沟道的导通时间减小,这样允许工作的开关频率就可以提高;

(2)沟槽宽度小,沟道完全开通所加的G极电压可以降低,导通更容易,开关损耗降低;

(3)沟槽宽度减小,沟道导通电阻降低,也更一进降低导通损耗。

正因为这些优点,也驱使半导体制造公司不断的采取新的工艺,追求更低的工艺尺寸,来提升半导体器件的性能、降低功耗。

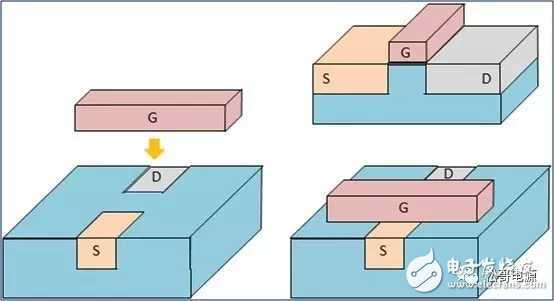

图2:变形的平面横向导电MOSFET结构

图2右上角为平面MOSFET的结构,实际的结构稍微变形,如图2下方的所示,G极同样也是跨在D和S之间,G极下面为绝缘的氧化层。

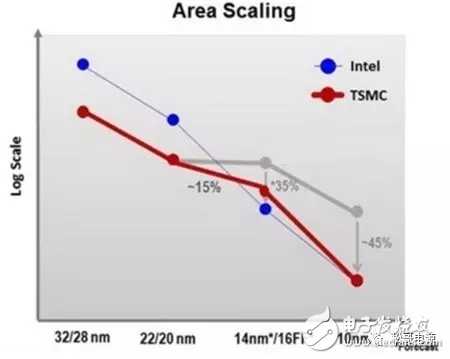

同一代技术,半导体生产的二大巨头英特尔和台积电,采用的线宽稍有差别,如下图所示。

图3:英特尔和台积电工艺

2、传统平面结构的限制

近些年来,半导体工艺不断的向着微型化发展,基于传统平面MOSFET结构的晶胞单元不断的缩小,漏、源的间距也不断的减小,G极下面的接触面积越来越小,G极的控制力就不断的减弱,带来的问题就是不加栅极电压时漏源极的漏电流增加,导致器件的性能恶化,同时增加了静态的功耗。

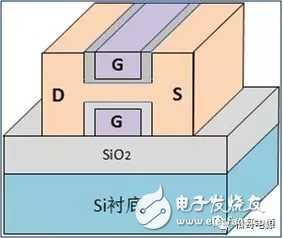

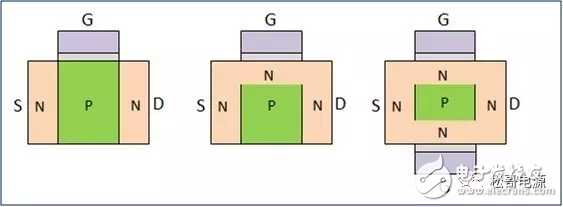

增加G极面积的方法,就必须采用新的结构,如三维结构。三维的G极结构有二种类型:一是双栅极结构,二是Fin型结构,也就是非常有名的鳍型结构,如下图所示。

(a):双栅极结构

G极不加电压 单G极加电压 双G极加电压

(b):导通沟道

图4:双栅极结构及导通沟道

双栅极结构形成二个沟道,减小沟道的导通电阻,增强了通流的能力和G极对沟道的控制能力。

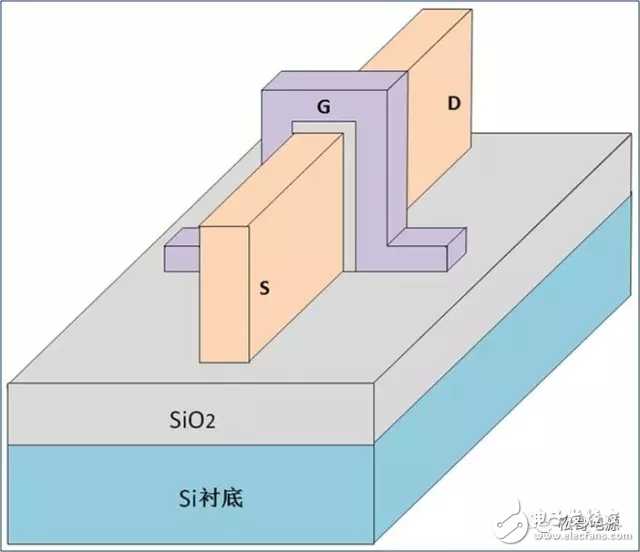

图5:Fin鳍型结构

FinFET结构看起来像鱼鳍,所以也被称为鳍型结构,其最大的优点是Gate三面环绕D、S两极之间的沟道(通道),实际的沟道宽度急剧地变宽,沟道的导通电阻急剧地降低,流过电流的能力大大增强;同时也极大地减少了漏电流的产生,这样就可以和以前一样继续进一步减小Gate宽度。

目前三星和台积电在其14/16nm这一代工艺都开始采用FinFET技术。

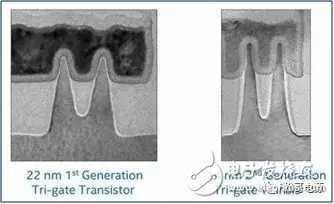

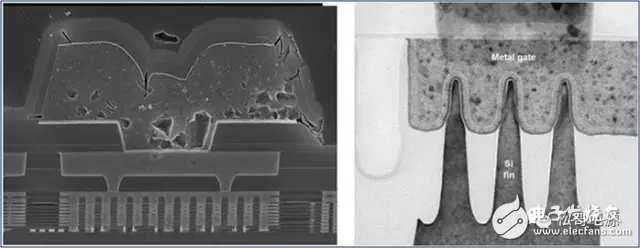

图6:Intel(左:22nm)和Samsung(右:14nm)Fin鳍型结构

注:图3、图6的图片来于网络。