理解功率MOSFET的寄生电容

功率半导体的核心是PN结,当N型和P型半导体结合后,在结合面处的两侧形成空间电荷区,也称为耗尽层,当PN结两端的电压变化的时候,PN结的空间电荷区的电荷也发生改变;另外,N区电子和P区空穴因为浓度的差异相互扩散,也会在PN结的两侧产生电荷存储效应,这些因素作用在一起,在任何半导体功率器件内部,就会产生相应的寄生电容。

MOSFET的寄生电容是动态参数,直接影响到其开关性能,MOSFET的栅极电荷也是基于电容的特性,下面将从结构上介绍这些寄生电容,然后理解这些参数在功率MOSFET数据表中的定义,以及它们的定义条件。

1、功率MOSFET数据表的寄生电容

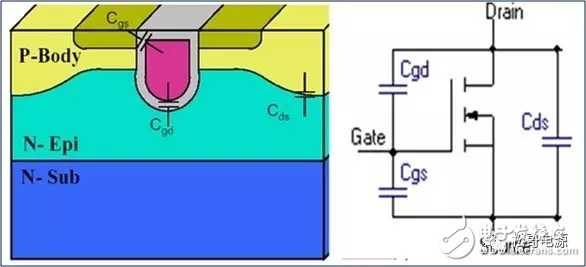

沟槽型功率MOSFET的寄生电容的结构如图1所示,可以看到,其具有三个内在的寄生电容:G和S的电容CGS;G和D的电容:CGD,也称为反向传输电容、米勒电容,Crss;D和S的电容CDS。

图1:沟槽型MOSFET寄生电容

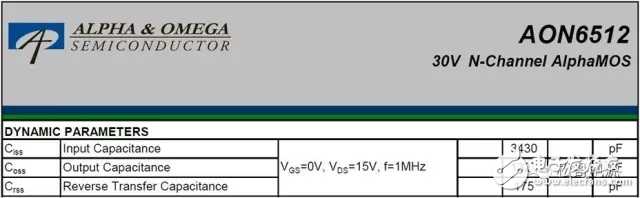

功率MOSFET的寄生电容参数在数据表中的定义如下图所示,可以看到,它们和上面实际的寄生参数并不完全相同,相应的关系是:

输入电容:Ciss=CGS+CGD

输出电容:Coss=CDS+CGD

反向传输电容:Crss=CGD

2、功率MOSFET寄生电容测试

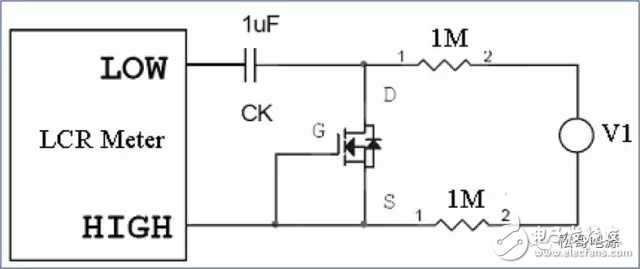

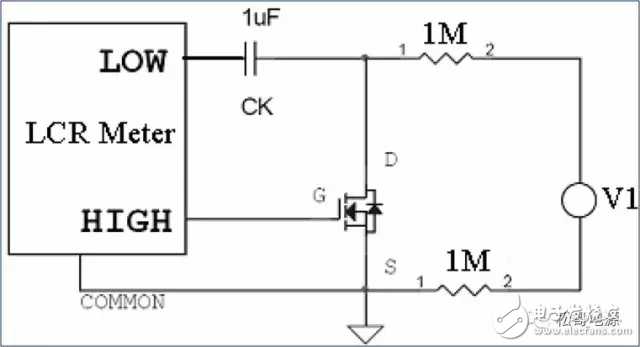

寄生电容的测试的条件为:VGS=0,VDS=BVDSS/2,f=1MHz,就是使用的测量电压为额定电压的一半,测试的电路所下图所示。

(a) Ciss测试电路

(b) Coss测试电路

(c) Crss测试电路

(d) 标准的LCR

图2:寄生电容测试电路

功率MOSFET栅极的多晶硅和源极通道区域的电容决定了这些参数,其不具有偏向的敏感度,也非常容易重现。

沟槽型功率MOSFET的寄生电容和以下的因素相关:

? 沟道的宽度和沟槽的宽度

? G极氧化层的厚度和一致性

? 沟槽的深度和形状

? S极体-EPI层的掺杂轮廓

? 体二极管PN结的面积和掺杂轮廓

高压平面功率MOSFET的Crss由以下因素决定:

? 设计参数,如多晶硅的宽度,晶胞斜度

? 栅极氧化层厚度和一致性

? 体水平扩散,决定了JFET区域的宽度

? 体-EPI和JFET区域的掺杂轮廓

? 栅极多晶硅掺杂通常不是一个因素,由于其是退化的掺杂;JEFET区域的宽度,JFET轮廓和EPI层掺杂轮廓主导着这个参数

高压平面功率MOSFET的Coss由以下因素决定:

? 所有影响Crss参数,由于它是Coss一部分

? 体二极管PN结区域和掺杂轮廓

3、功率MOSFET寄生电容的非线性

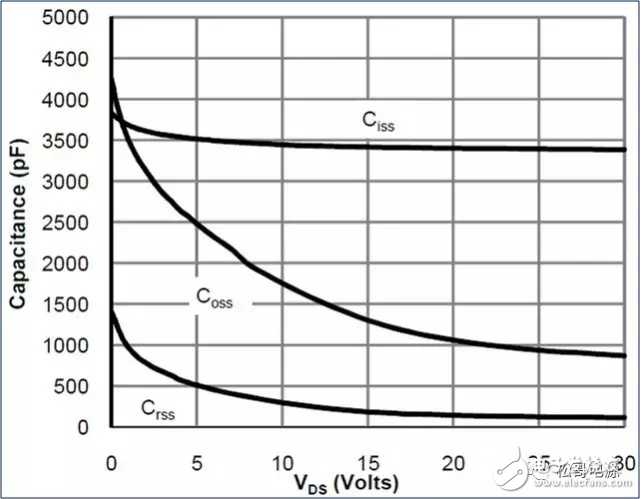

MOSFET的电容是非线性的,是直流偏置电压的函数,图3示出了寄生电容随VDS电压增加而变化。所有的MOSFET的寄生电容来源于不依赖于偏置的氧化物电容和依赖于偏置的硅耗尽层电容的组合。由于器件里的耗尽层受到了电压影响,电容CGS和CGD随着所加电压的变化而变化。

图3:AON6512电容随电压变化

电容随着VDS电压的增加而减小,尤其是输出电容和反向传输电容。当电压增加时,和VDS相关电容的减小来源于耗尽层电容减小,耗尽层区域扩大。然而相对于CGD,CGS受电压的影响非常小,CGD受电压影响程度是CGS的100倍以上。

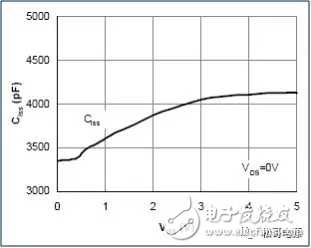

图4显示出了在VDS电压值较低时,当VGS电压增加大于阈值电压后,MOSFET输入电容会随着VGS增加而增加。

图4:输入电容随VGS变化

因为MOSFET沟道的电子反形层形成,在沟漕底部形成电子聚集层,这也是为什么一旦电压超过QGD阶级,栅极电荷特性曲线的斜率增加的原因。

所有的电容参数不受温度的影响,温度变化时,它们的值不会发生变化。

好资料 很有帮助 好好学习