看图说EMC

时间:10-02

整理:3721RD

点击:

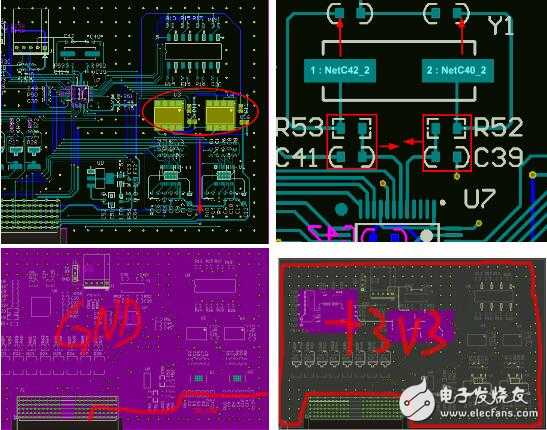

上图:

1.光耦隔离芯片放置到单板中间且没有掏空和做隔离处理;

2.晶振信号走线太长太绕,周边都没有放置地过孔;

3.地平面层没有分割处理;

4.电源层被分割放置了两种电源,导致BOTTOM层走线跨分割;

5.整个单板中地过孔放置都很少;

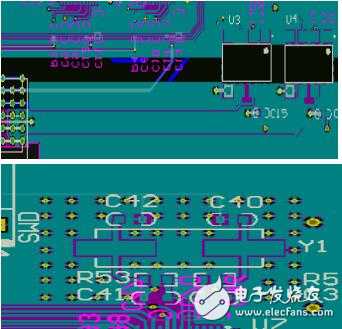

修改后的PCB设计,如上图:

1.隔离芯片向下摆放,芯片下面掏空,

2.调整晶振信号布线,通过包地方式处理,降低信号对外产生辐射;

3.地平面做了分割处理,且保证了地平面的完整性;

4.电源层铺设了一种主电源,保证了电源的完整性,避免BOTTOM层走线跨分割;

5.且在单板空余地方和高速信号周边按按400MIL间距打地孔处理,保持网络较好的连通性和减小地的环路面积降低阻抗;

点评:为了SI和PI的完整性,地平面和电源平面一般要保持完整,不要分割的很零碎导致跨分割现象;隔离芯片投影区下均要掏空,避免隔离前后信后之间的耦合产生干扰,时钟布线尽量类差分且短而粗(降低阻抗)。

关于赛盛技术:

成立于2005年,专注电磁兼容(EMC)等工程技术,为企业提供产品电磁兼容(EMC)问题整改、产品电磁兼容设计、电磁兼容技术培训、体系建设咨询服务。

进来看看