开关电源的控制环截止频率和开关频率之间的关系

开关电源的控制环截止频率和开关频率之间的关系是个很专业的问题,非电力电子专业的小伙伴看不懂很正常。而且如果不搞这行的话,私下觉得其实也完全没有搞懂这个的必要,╭(╯^╰)╮但是我能说其实就算搞这行的懂变换器的建模和控制的也是凤毛麟角么。

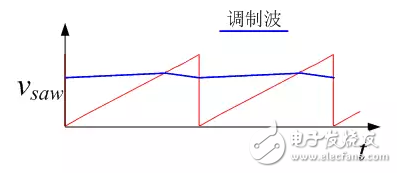

1、香农采样定理 看到这个定理,估计第一反应就是联想到信号与系统、数字信号处理、ADC采样blabla,但绝对联想到不到电力电子变换器,香农采样定理和电力电子变换器扯上关系又是什么鬼?且听我细细道来。对于电力电子变换器来说,占空比是最终的控制信号。而调制波和载波交截确定了占空比,那么占空比是由调制波确定的,这句话对么?Not exactly,精准的说法是,调制波与载波的交截点确定了占空比。 请和我一起大声念三遍:交截点!交截点!交截点! 如图1,两个调制波显然是不一样的,但是他们和载波的交截点一样,那么占空比就一样,最终的控制效果就一样,由于PWM环节的存在,两个调制波的差异信息仿佛丢失了一般。看出点什么了没?这其实不就是采样么?采样的特点是什么?就是只能得到采样时刻的信息,而两次采样之间的信息是丢失的,这也不正是PWM环节的特点么?所以电力电子变换器本质上是一个离散采样系统。

图1

由于是采样,那么自然有香农采样定理,香农采样定理告诉我们,电力电子变换器输出电压的频率是有上限的,理论上最高是开关频率(载波频率)的一半。其实想想现实中存在的变换器,是不是恍然大悟了?一个开关频率为100kHz的变换器,你可以让他输出直流(0频率),输出50Hz(并网逆变器),400Hz(航空变流器),但有没有听说一个开关频率为100kHz的变换器能输出可控的100kHz的正弦波的?没有吧(如果有,我们实验室做ET电源的那位美女师姐和帅哥师弟要开心死了。)。这其实和环路截止频率为开关频率的1/5~1/10没啥关系,哪怕你环路截止频率再高,也不可能输出开关频率一半频率以上的电压,这是由采样系统本质决定的。(注:上述讨论的是最简单最普遍的变换器,不考虑多电平、载波移相、MMC等结构,那些拓扑结构是有可能使得输出电压的频率极大地逼近开关频率,但这些结构的本质和我上面说的完全不是一回事,不影响我上面分析的正确性,这个展开来说就太多了,这里懒得写了,懂的自然懂)

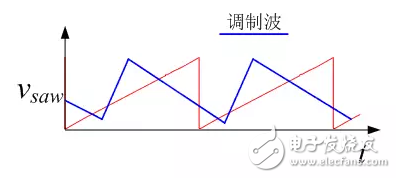

2、调制波与载波多次相交这个叫斜坡匹配原则。正常情况下调制波和载波应该这样:

图2

而当调制波上升的斜率超过载波上升斜率时,就会进入不正常的状态,比如这样(即题主所说的多次交截):

图3

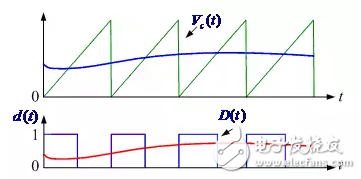

所以说,要降低环路的截止频率,使其能够很好地抑制开关次的纹波,使得调制波的上升斜率不超过载波的上升斜率,这确实是可以算模拟控制中环路截止频率为开关频率的1/5~1/10的原因之一。但数字控制不存在这个问题,数字控制由于零阶保持器的存在,调制波在一个周期内是保持不变的,斜率恒为0,如图4,不存在斜率匹配的要求

图4

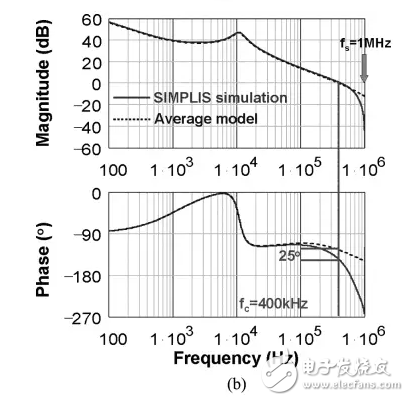

3、小信号模型的准确性这个问题很关键,其实准确的说法是,状态空间平均法的准确性。我们来看下状态空间平均法对PWM环节的处理。

图5

假设一个电力电子变换器开关频率为100k,调制波频率为10k,那么经过PWM环节得到占空比,状态空间平均法认为得到的占空比也是一个10k的交流信号(如图5所示的红线),即PWM环节等效为一个比例环节。但实际上不完全是这样的,对占空比做傅里叶分析,可以知道占空比中除了10k的分量外,还有90K,110K,190K……的分量,那么状态空间平均法的准确度就依赖于这些非基波分量的抑制程度,显然,带宽越低,对这些非基波频率的分量抑制能力越强,状态空间平均法得到的模型就越准确。这是电力电子变换器环路截止频率为开关频率的1/5~1/10的重要原因之一,我实验室有个同学就做这方面研究的,他告诉我,当环路截止频率超过开关频率的1/5以后,用状态空间平均法得出的模型就和实际模型差距比较大了。当然,也有考虑边带频率来建模的,这就是多频率模型,当然该模型的复杂程度是远远大于状态空间平均法得到的模型了。但该模型也有实际的应用场合,比如在VRM中,要求变换器动态响应非常快,那么往往就需要环路截止频率为开关频率的1/3甚至更高,这时候状态空间平均法完全无法指导设计了,必须要用多频域模型。贴一张CPES关于多频率模型的研究成果,可以看到随着带宽提高,状态空间平均法和实际模型差距越来越大。

图6

当然我们实验室专门研究建模的同学(我们都喊他教授)有更准确的模型,但是还没有publish出来,所以我这里不能提供啦。

4、数字控制的延时问题这个问题也很重要,不同于模拟控制,数字控制由于存在零阶保持器和一拍滞后,总共会在环路中引入1.5拍滞后,如图7所示。

图7

1.5拍滞后是什么概念呢?

就是如果采样频率等于开关频率,在环路中会引入540*f/fs的相位滞后,也就是说,在开关频率处会引入540度的相位滞后!即使截止频率是开关频率的1/10,光是数字控制在截止频率处也会引入54度的相位滞后,其实也很难补偿回来了。所以说,在数字控制下,为了保持控制系统有足够的相角裕度,其截止频率会更低一些,从而减小数字控制引入的相角滞后的影响。当然还有一种办法是提高采样频率,现在我们做逆变器一般采样频率是开关频率的两倍。这也是为了减小数字控制造成的延迟。 (+﹏+)~

idtjklyterwertyioopiyerto

东西好 但看不懂