问一个fifo的问题读写问题。

时间:10-02

整理:3721RD

点击:

之前一直没有用到过fifo,觉得应该是很简单的事情,但是有一段不愉快的小插曲,它仍在我的脑海中余音绕梁。

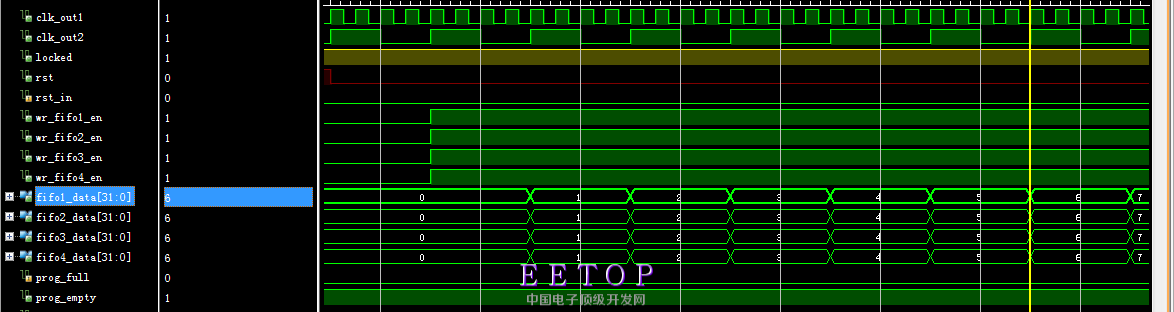

事情是这样的。一个异步的fifo,读是写的4倍,读写时钟同源,由MMCU产生。我把0,1,2,3......写进fifo中,但是当读取fifo时,读到的数据却是0,2,3,4,5.............把1给漏掉了,我实在是想不清楚原因,到底应该怎么纠正。

贴图,一目了然。

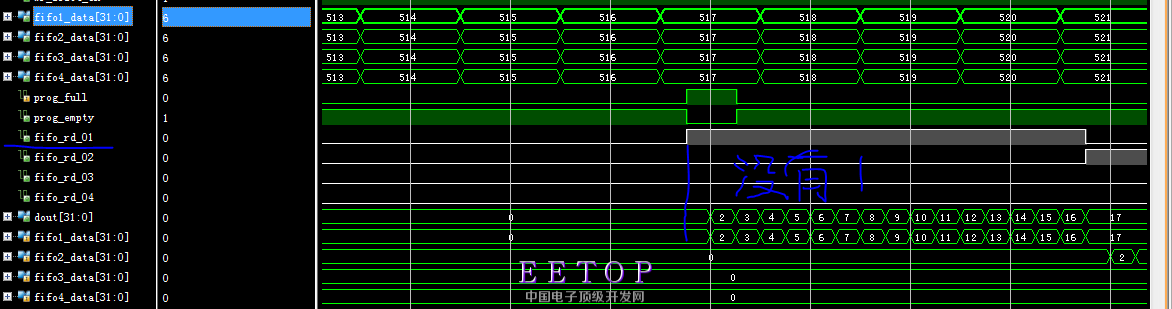

还有一个问题呢。就是prog_full,prog_empty.当我生成ip核时,不生成prog_empty,只生成prog_full时,只要fifo一有时钟,就会置1,但是我设置的数值是512,这据我的一个朋友说是初始化造成的,很常见,可以加上其他的约束条件,比如非空来控制。后来我同时生成prog_full,prog_empty,还是同样只用prog_full,倒是不会出现前面的问题了。

当然重点集中在第一个问题。我实在是无从下手,可能是什么问题。

事情是这样的。一个异步的fifo,读是写的4倍,读写时钟同源,由MMCU产生。我把0,1,2,3......写进fifo中,但是当读取fifo时,读到的数据却是0,2,3,4,5.............把1给漏掉了,我实在是想不清楚原因,到底应该怎么纠正。

贴图,一目了然。

还有一个问题呢。就是prog_full,prog_empty.当我生成ip核时,不生成prog_empty,只生成prog_full时,只要fifo一有时钟,就会置1,但是我设置的数值是512,这据我的一个朋友说是初始化造成的,很常见,可以加上其他的约束条件,比如非空来控制。后来我同时生成prog_full,prog_empty,还是同样只用prog_full,倒是不会出现前面的问题了。

当然重点集中在第一个问题。我实在是无从下手,可能是什么问题。

我是觉得你0和1其实都没有写进去,我不知道你生成时候的具体参数是什么,你看看手册,读的时候数据是和fifo_rd_01一起出来的还是会延迟一个cycle

我怀疑你的问题是出在rst上面,你仔细看看手册,rst释放到fifo可以开始正常工作需要隔多久时间,你可以试着rst释放之后隔10个cycle再去操作fifo试试看

问题诚如您所说。我复位结束后又延迟了256个时钟,结果就正确了,具体最小延迟是多少,我也没有试,

另外,据我的观察,读使能之后的一个时钟之后才能读到正确的第一个写入fifo的数据。

这里就又有一个问题。怎么处理?

always@(posedge clk)

if(rd_fifo_en)

begin

if(cnt==1)

begin

cnt<=cnt;

data_in<=fifo_out;//一个时钟之后再读取fifo中的数据。

end

else

cnt<=cnt+1'b1;

end

感觉好愚蠢的程序。

也可以用一下valid。

0和1没写进去,因为外部rst虽然释放了,但是rst进fifo后要进行处理,最后fifo里边实际用到的rst释放比外部rst晚几个时钟周期,貌似是3个,可以看fifo ipcore的使用手册。

恩,谢谢您的回答,非常有用。