PCIE 总线的传输速度问题

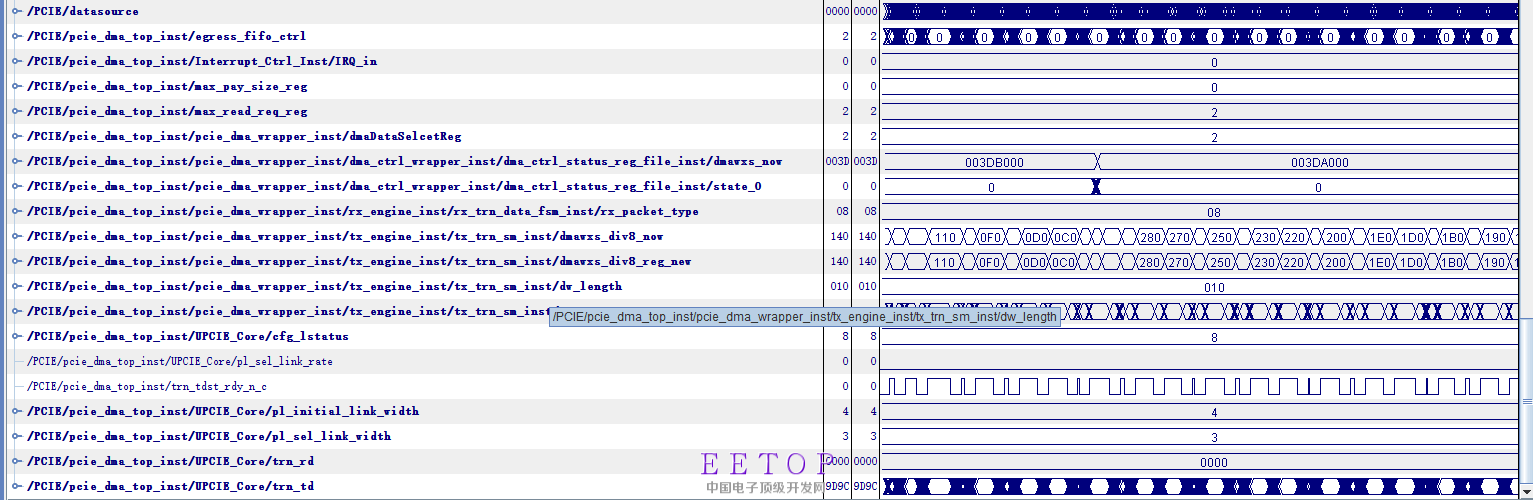

通过查看信号发现,trn_tdst_rdy_n有一半以上的周期都是无效的,无法传输数据。通过查看信号查看链路信息

pl_initial_link_width,pl_sel_link_width等显示的当前训练好的链路也都是x8,希望高手解答如何提高传输速率,以及信号

trn_tdst_rdy_n有一半多周期无效的原因

欢迎大家讨论,多提点意见,目前pcie dma TLP 每包128B,为了提高速度,也可以提高一下每包的长度,就是目前觉得影响速度的原因还是trn_tdst_rdy_n 信号无效的周期过多,trn_tdst_rdy_n代表ip可以接受trn_td的数据,是ip核给出的信号,想知道一下这个信号受什么控制,收不收pc端的影响,

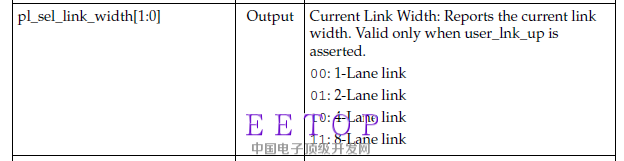

trn_tdst_rdy_n信号,受不受pc端驱动的,或者pc端性能的影响,还有一个 pl_sel_link_width显示当前链路为x8代表当前的传输速度就是x8的速度吗?

我测试的4x、2.5g速率下 DMA写能到790MBps,如果你的是x8的 那你的速度就有点低了。其实提高DMA速度最明显最简单直接的方法就是增加DMA长度。我是在DMA长度=2MB下测的。payload=128B这个不是说你想提就能提的,还要看对端设备支持不支持。

另外,你确认下经过协商后你的链路宽度到底是不是x8的。如果是x4, 780的速度已经很高了。 因为4x、2.5g的速率,去掉10b/8b编码后,理论极限速率是1GBps,但是每个数据包还有开销,比方说TLP头,数据链路层加的序列号和CRC等等,再加上你的DMA机制所消耗的一些时钟周期,能有80%(800MBps)的效率就已经不错了。

非常感谢您的回答,我想要知道一下怎么确定链路的宽度

我当时查的是pl_sel_link_width信号,当前采用的链路宽度,显示的是11链路为x8,

trn_tdst_rdy_n,无效周期超过一半以上,如果是 x8的话应该没有那么多的无效周期,所以我当时怀疑的方向有两个:

1、link_width;

2、另外一个就是pc侧的问题;我测试用的pc电脑性能比较低,而trn_tdst_rdy_n是pcie给出的信号,只要ip内部的

buff不满的情况下,这个信号都是有效的,代表可以接受tx发送的数据,就是想问一下,pc侧性能会不会也会影响trn_tdst_rdy_n

的信号

pl_initial_link_width 有个这个信号 这个应该是协商后的 最终的链路宽度 还有一种方法是 读取pcie设备的配置空间的Link status寄存器,有Negotiated Link Width 比特位

good,3x

- 有大神会 pcie总线的么(1970-01-01)

- 我要做一个isa总线控制器(1970-01-01)

- +5V供电的EPM7128S可以和3.3V供电的基于PCI总线的芯片直接接口吗? (无内容)(1970-01-01)

- 讨论一下:PCI 总线开发(1970-01-01)

- 请教关于Avalon总线的问题(1970-01-01)

- 搞不懂,ALTERA的CPLD双向数据总线怎么仿真? (无内容)(1970-01-01)