xilinx SPARTAN6的时钟输出质量问题

时间:12-26

整理:3721RD

点击:

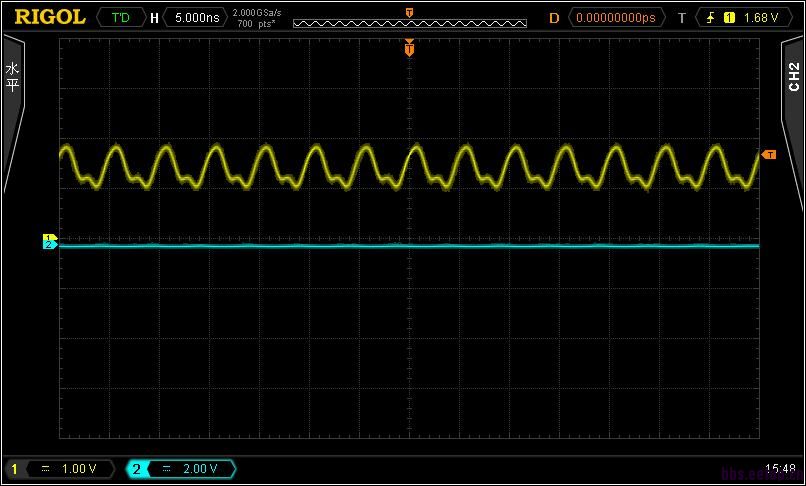

输出时钟频率为200Mhz,高电平只有2V,低电平有1V,时钟输出已经配置为ODDR2,也采用了REG类型,电平就是达不到要求,管脚配置为NET "vout_pclk"LOC = A8 | IOSTANDARD = "LVCMOS33" | OUT_TERM = UNTUNED_50;去掉输出内部端接50R,现象一样,求助大家了!

1.看看io对应bank的vcco电压是不是3.3v

2.是不是示波器没有量对

BANK电压是3.3v,同时量其他的输出信号正常高可达3.3v,低差不多0V

你的时钟进FPGA的电平标准是多少?有没有测一下正常不?看你的输出时钟像是LVDS18

1.确认你的测量仪器的带宽是否可以满足测量要求

2.确认你使用的BANK是否正确,BANK电压又是否正确

sp6的IO输出很糟糕的,这个我也试过

输出200M的到没有试过,40M的试过波形挺好的,板子的问题?

输出110MHz以内都正常,波形也还可以,超过120MHz就不行了,希望输出的时钟频率为185Mhz

- XILINX可编程逻辑器件设计技术详解—何宾著(1970-01-01)

- xilinx spartan原版英文教程(1970-01-01)

- 基于XILINX FPGA的OFDM通信系统基带设计—史治国(1970-01-01)

- Xilinx ISE 12.2 调用 Modelsim 进行行为仿真详解(1970-01-01)

- 大神进来坐坐,小弟有一事要问,有关FPGA图像采集(1970-01-01)

- 求教大神!xilinx,GTX,7 Series FPGAs Transceivers Wizard数据传输问题(1970-01-01)