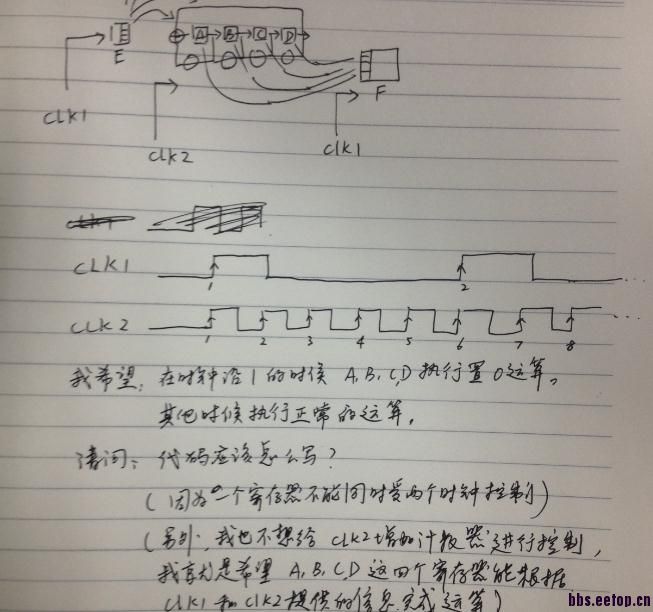

用两个不同的时钟控制同一个寄存器的问题(我写在纸上了),再发一次

A,B,C,D是用clk2控制的寄存器,E,F是用CLK1控制的寄存器。

晕,写错了,图中6,7,8改成1,2,3.

寄存器就使用CLK2,然后把CLK1当成同步复位信号来用。

reg reg0,reg1;

wire rst0, rst1;

wire clk0, clk1;

wire in_buff, out_buff;

always @ ( posedge clk0 or negedge rst0)

if ( ~ rst0 )

reg0 <= reg1;

else

reg0 <= in_buff ^ reg1;

always @ ( posedge clk1 or negedge rst1)

if ( ~ rst1 )

reg1 <= ~ reg0;

else

reg1 <=reg0;

assign out_buff = reg0 ^ reg1;

我想把clk1左移一个周期,然后把它看成clk2的条件来处理。

个人认为,能让寄存器只工作在clk2, 把CLK1当条件或控制信号是比较合适的解决方案。

寄存器工作在不同时钟域,都是在clock控制模块切换时钟,然后寄存器端口只看到一个clock信号。

clk1与clk2有没有关系?如同源派生。

如果没有关系,问题还是存在的。

如果是同源派生,根本就不用这么复杂了。

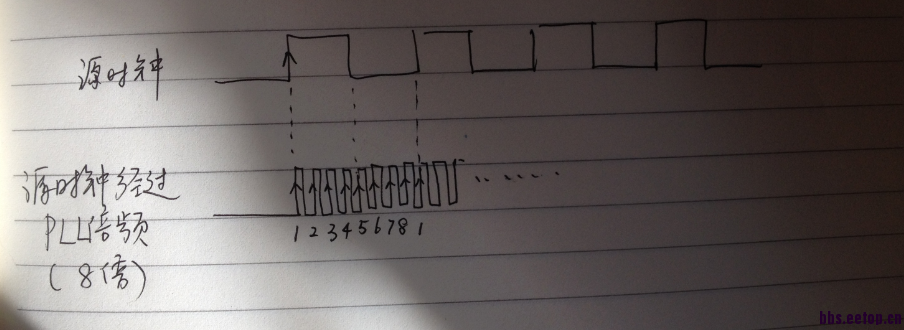

同样的问题,但是这次我希望将低频时钟经过PLL倍频得到8倍频的高频时钟,然后希望用高频时钟控制串行迭代电路(高频时钟的第一个沿 执行的任务和 其他几个沿不一样,怎么能让高频时钟 利用 源时钟的信息?)谢谢

我们采用PLL将参考时钟倍频后,一般不再同时采用原来的参考时钟与PLL输出,因为PLL输出与参考时钟的相位关系没法明确固定,当然PLL的多路输出之间的相位关系是可以确定的。

可以将PLL输出按需要输出状态机信号去用作使能或同步复位信号。

你的图里可以将pll输出8分频,派生使能信号。

那我可不可以让PLL输出一个和输入时钟一样的波形,再输出一个 输入时钟的 8分频,并确定他们之间的相位关系呢?比如说,我写了一个module,module里面生成一个信号a。

然后,我像下面这么写:

always@(posedge a)begin

........

end

请问,这个a信号是不是不会利用任何的时钟资源(BUFG之类的),而是仅仅作为普通的信号传递到各个寄存器的时钟端?(我试了一下好像是这样的,而且我人为添加BUFG原语,最后也没综合出BUFG来)。

这就引出一个问题,是不是只有"设计最顶层的"那个模块的输入信号 才可能 利用到 时钟资源?(就是说只有那些 ”顶层模块的端口信号“ 的 后面 才可能接上BUFG之类的东西?)

于是,我就想,现在我想利用PLL的输出去驱动整个器件的运行,不知道PLL的输出是不是会 经过一个BUFG。

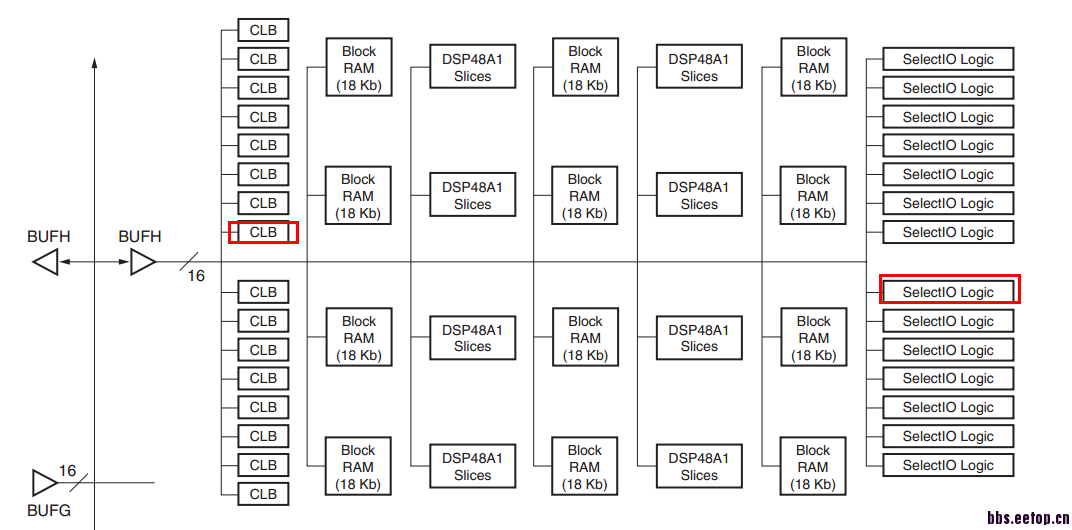

我看了xilinx关于时钟资源的文档,里面有两张图,没太看懂:

你看啊,图中的PLL是不是也有端口通到整个FPGA的外面 ,用于接收时钟信号?然后传给整张图中心的BUFG呢?

还有一张图:

这张图是上面那种图中水平时钟线的具体化,我就是想问一下那个CLB是不是就是包含很多Slice,然后那个SelectIO是不是就是IO端口的意思?

是可以的。

实际上,一个PLL系统的所有输出(包括内部参与相位比较的时钟)都是由VCO输出的频率非常高的时钟信号通过不同分频节点输出,

它们之间由于是同源派生,所有相位关系是确定的。有的PLL系统输出时钟的相位甚至可以配置(与分频系数有关系的)

你说道情况完全可以实现。

PLL到PAD应该是特定的专用脚,是全局的时钟输入输出脚,不是普通IO。BUFG应该在全局时钟布线资源里面,到Slice是驱动IOBlock里面的Flip-Flop的,只能用作时钟,触发寄存器;不是用于输出的,也不能用作普通的wire信号,参与组合逻辑。

- Quartus II 代码综合后,为什么寄存器CLRN端的RTL和Technology Map...(1970-01-01)

- wire 与 reg 区别(1970-01-01)

- 夏宇闻那本书的EEPROM程序 感觉程序根本就不能进入读操...(1970-01-01)

- DE2-70 EP2C70F896C6 数码管引脚分配的时候段码不是公用的吧(1970-01-01)

- FPGA基础学习笔记--时序逻辑电路-寄存器(1970-01-01)

- 串入并出移位寄存器出现问题?(1970-01-01)