DDR3的read-to-write延迟

时间:12-26

整理:3721RD

点击:

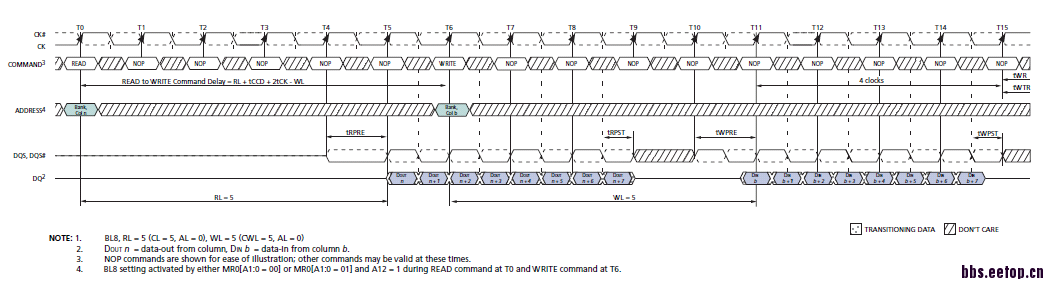

从手册上读到的DDR3读命令到写命令延迟为:

BL8:RL + tCCD + 2tCK - WL

BC4:RL + tCCD/2 + 2tCK - WL

不知道是怎么得出的,求解释!

非常感谢!

BL8:RL + tCCD + 2tCK - WL

BC4:RL + tCCD/2 + 2tCK - WL

不知道是怎么得出的,求解释!

非常感谢!

应该有时序图吧

嗯,仔细揣摩了一下,猜测大概是这样的:

从发出Read命令后的RL时间,第一个读数据出现在data bus上;再经过tCCD的时间(对于BC4是tCCD/2),所有的读数据都被发送到data bus上;然后需要2个周期的时间来建立DQS信号,即2个周期后第一个写数据可以发送到data bus上。因此,从Read命令下发到第一个写数据出现在data bus上经历了RL+tCCD/2+2个周期,减去WL就是Write命令发送的时间,即Read-to-Write延迟。

不知道我理解的对不对……

write 相关文章:

- 询问altera的write2flash.exe(1970-01-01)

- 求助modelsim仿真警告: read_during_write_mode_mixed_ports is assumed as OLD_DATA(1970-01-01)

- 急急急!fwrite输出有符号?(1970-01-01)

- 版主请教_how to write script(1970-01-01)

- SDRAM 的 write recovering 到底是什么意思?(1970-01-01)

- 请问DC中write的问题(1970-01-01)