关于synplify FPGA综合时关于Clock Gate 的问题

来降低功耗,但是这个功能在ASIC中通过工艺相关的IP实现,在FPGA 做Emulation时 想实现该功能,

但是印象中FPGA用的全局时钟树结构,怎么做Clock Gate 另外写一个逻辑来实现吗,如果

另外写一个行为逻辑,在FPGA具体实现上是怎么样的,是否完全靠 routing resources 实现了?

如果是的话 在synplify_primer_dp中的Fix Gated Clock 和 Fix Generated Clock会对其做怎样的优化?

xilinx vertex 4的板子 xilinx 是否允许用户干预全局时钟树..?

各位兄弟,只要有想法就请留下看法。谢谢。

xilinx没法做clock gating setup/hold检查。节哀

愿闻其详...

可以试试

路过的各位 有何看法?

小编是做ASIC的FPGA验证吧?我也是做这个,同时也要实现AISC中的gated clk。

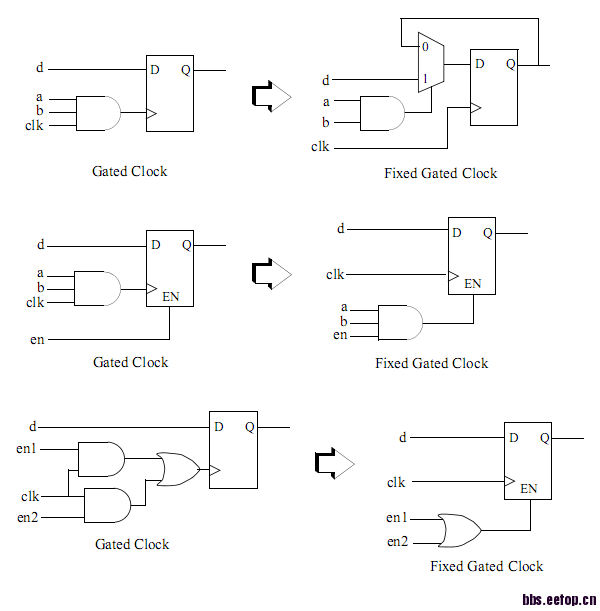

使用synplify综合,勾选fixed gated clk。该选项会将门控时钟改为时钟使能,即用规模换取时钟同步:

当gated clock之后的触发器太多时,synplify不可能完全同步gated clock。fixed的结果可以在log中查到。

当gated clock不能修正时,很可能gated clock前后形成两个时钟,这时候就靠在implemention中加约束,尽量将关键的时钟放到全局时钟上。全局时钟可以手工例化,但效果很差,会影响到其他部分的布局布线,不建议使用。

当geted clock增加到一定数量时,工具无法满足时序要求。我的做法是减少gated clock数量,减少的gated clock部分让digital仿真验证去吧,我没办法了。

对这个不是很了解,学习了。..........

不过看上面的意思是FPGA中会将clock的门控信号改成使能信号?

是这样,工具自己做。

fpga不适合实现asic中的复杂clock gating电路,因此在fpga中我们不做gating

非常感谢你的建议,回答很赞!谢谢...

非常感谢你的建议,回答很赞!谢谢...

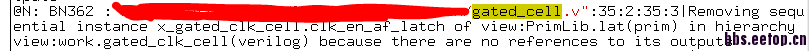

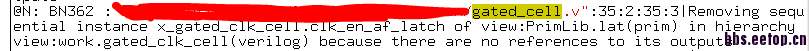

兄弟我在用synplify综合的时候报了warning如下:

我检查了相关的 gated_cell的输出逻辑 确定有负载的 ,这个问题你是否遇到过?

synplify的RTL view中存在相关的逻辑的,在technology view中 这部分就被remove了

何解?

以上 谢谢...

如果想关掉时钟 可以让时钟先过一个pll 不使用时将输出关断

fpga中是不能使用门控时钟的

更进一步了解问题之后,现在的问题描述如下:

when i use FPGA to do verification about ASIC's gated clock, this issues (clock gating) occurred , i use synplify_perimer_dp to synthesis ,

when i set "Fix Gated Clocks" as '0' the geted cell logic was existed exactly , but when i set "Fix Gated Clocks" as '3'

my geted cell module was removed,by waring:

"Removing sequential instance X of view:X because there are no references to its outputs "

I have checked all outputs from the module ,all of them are connected correctly

somebody help me ,thans a lot ...

看起来很高深的样子

将gate clock cell的属性改为“keep”,再跑synthesis看看。应该不会被remove。但是要跑下post syn仿真,确保出来的网表没啥问题

学习了,谢谢

thank u

谢谢分享!

FPGA synplify Gate Clock 相关文章:

- 旧版本生成的 DDR2 IP ,新版本的 MegaWizard 打不开。(1970-01-01)

- 写一段HDL代码实现对输入时钟三分频的功能(1970-01-01)

- FPGA多时钟设计(1970-01-01)

- 为什么FPGA时钟频率不高,却适合做高速处理?(1970-01-01)

- FPGA Verilog HDL 设计实例系列连载------交通灯的控制(1970-01-01)

- 基于VHDL的FPGA与NIOS_II实例精炼视频教程免费下载(1970-01-01)