xilinx的fifo读数不对

对xilinx的fifo核仿真一下看看咋用。发现没用对。还没找出问题。请教

fifo_16_1024 uut (

.rst(rst),

.wr_clk(wr_clk),

.rd_clk(rd_clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.wr_data_count(wr_data_count),

.rd_data_count(rd_data_count)

);

always#5 wr_clk =!wr_clk;

always#7 rd_clk =!rd_clk;

always#20 din = din+1'b1;

initial begin

// Initialize Inputs

rst = 0;

wr_clk = 0;

rd_clk = 0;

din = 32'd10;

wr_en = 1;

rd_en = 0;

// Wait 100 ns for global reset to finish

#100;

#100;

#100;

wr_en = 0;

#100 rd_en = 1;

#14rd_en = 0;

#50 rd_en = 1;

#14rd_en = 0;

#50 rd_en = 1;

#14rd_en = 0;

#50 rd_en = 1;

#14rd_en = 0;

#50 rd_en = 1;

#14rd_en = 0;

// Add stimulus here

end

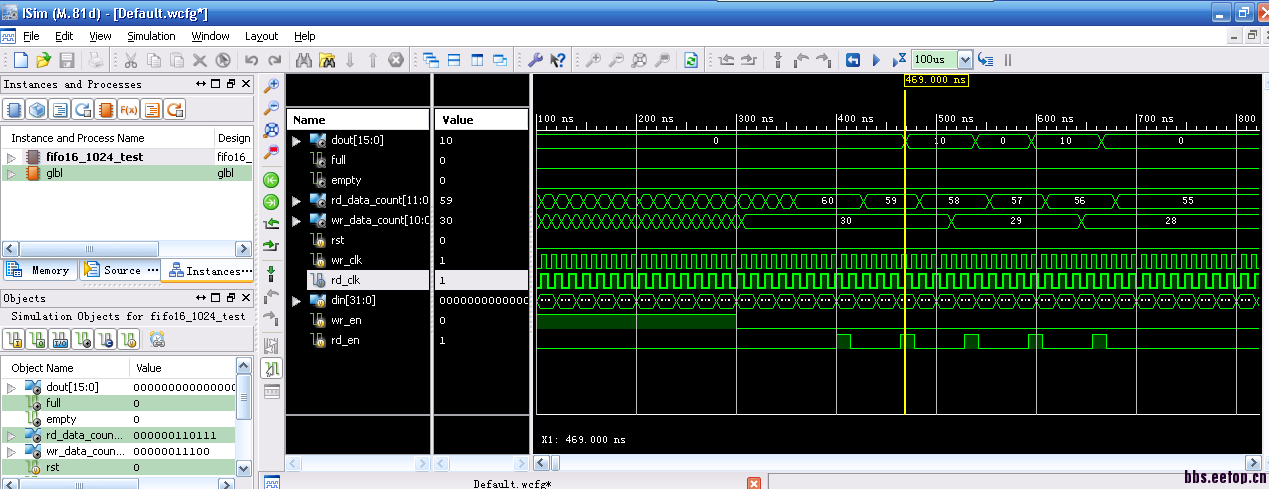

1)看到里面那rd_count确实在4个读使能后减了4

(2)但是为啥4个读使能只跑出了两个dout?

(3)数据从10开始。就算读出两个。应该也是1011。为啥是两个10我就不能明白了。

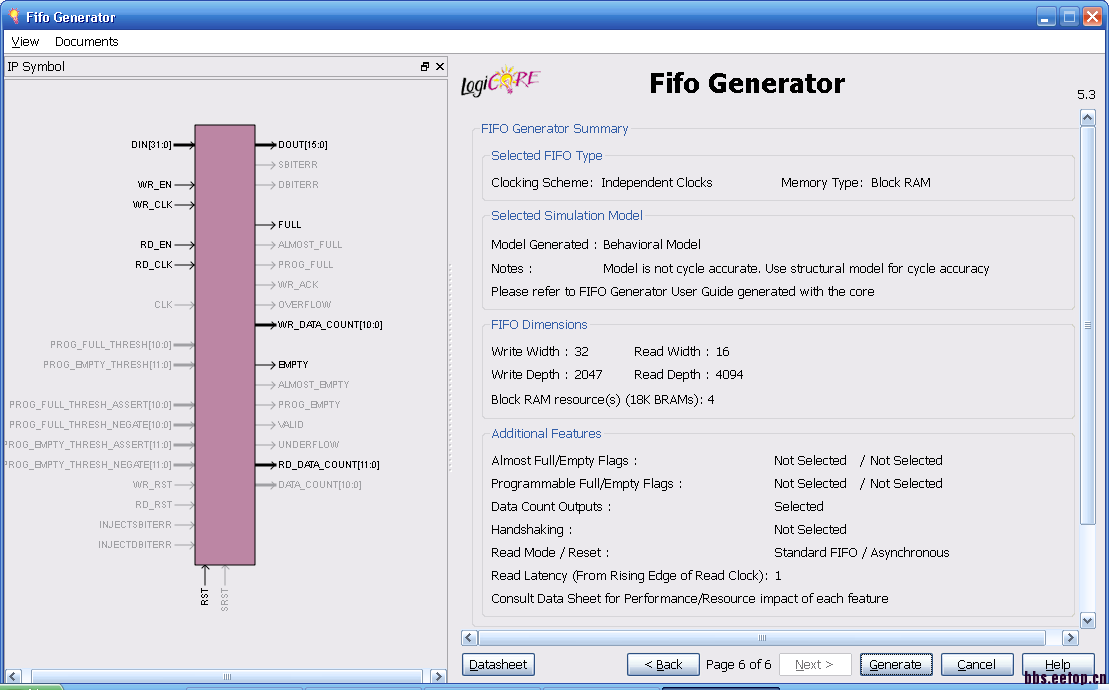

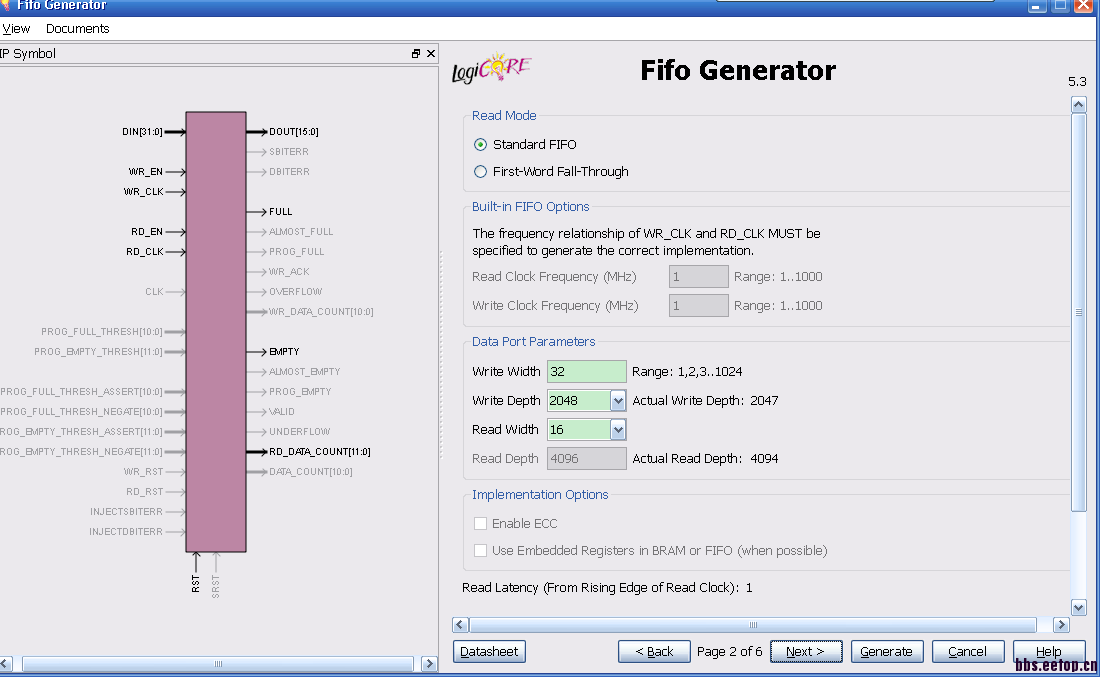

fifo有两种模式,你选择的是哪种?

是的,

第一个是你没有写进去把?

- SDRAM控制问题请教:为何用的器件模型读数据的时候是高阻Z(1970-01-01)

- 请教关于从memory中读数据的问题。望各位指教,谢谢了。(1970-01-01)

- 求助: SPI通信中配置成主模式是读数据问题(1970-01-01)

- xilinx FIFO IP核前仿和后仿读数据少了3个,真奇怪!(1970-01-01)

- 求助,关于ddr2 controller的问题,请问写数据和读数据的步骤应该是什么?(1970-01-01)

- RS232读数据之后写到RAM中的地址生成器不稳定(1970-01-01)