Quartus II可以不设置tsu,tco,tpd,th吗

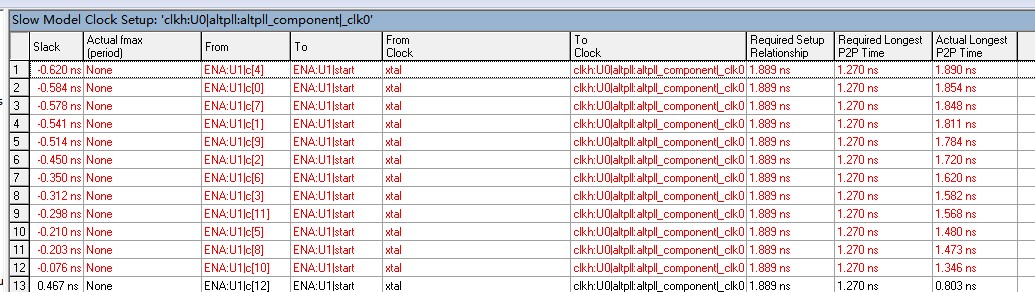

顶层图如上哈,在单独验证模块功能的时候ENA是时序违规的,但是加了前面的PLL和Trig之后就出现时序违规了,约束的话我只约束了XTAL(有源晶振输入)和PLLCLK0(晶振的8倍频,400MHz),违规文件如下哈

顶层图如上哈,在单独验证模块功能的时候ENA是时序违规的,但是加了前面的PLL和Trig之后就出现时序违规了,约束的话我只约束了XTAL(有源晶振输入)和PLLCLK0(晶振的8倍频,400MHz),违规文件如下哈

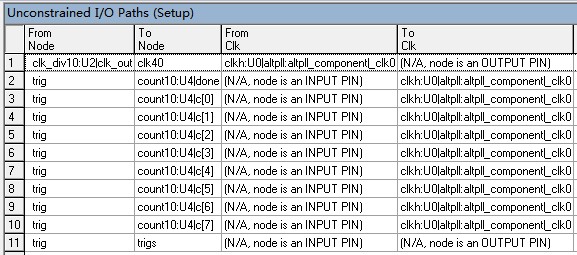

后来我又看了未约束的信号,是下面这些

我觉得是内部400MHz的时钟太高了,导致输入Trig与400MHz的建立时间不够,这样的话可以约束吗?

我这个设计的思路是用Trig触发10分频计数器,将400MHz(不需要与Trig相关)10分频成40MHz的输出时钟,同时输出Trig信号。

使用ENA这个模块的原因是Trig持续时长不够,我用ENA产生一个上升沿和Trig几乎一样(400MHz延迟10个周期)、持续时间要长的信号,作为10分频的使能信号(图中写成了reset)。

ENA用了两个时钟是因为只是用400MHz的时钟的话,要数20000下才满足Trig(经过延迟的信号,即10分频的使能信号) 的要求,所以我是用400MHz作为ENA内部计数器的起始,再用晶振的50MHz来计数4000下。

不知道这样说明白没有,欢迎大家发表自己的意见!

你如果不设,那么就会有系统预设的取代

你设太小,就会造成 400MHZ 警告很多,设太大很容易乱掉,看来只能指定讯号设置.

我也有一个问题,Quartus 警告,说我的某只脚是 clk,但是我查过不是 clk ,不知道怎么处理?

信号不是clk这个情况好办,在Assignment Editor里面的To那里选定你的那个信号,然后Not A Clock改成on就行了

内部使用400M的clk,太高了吧。

可以不设的

但是 Quartus 说的是一个 REG,非接脚(PIN).

例如:

Warning (332060): Node: I2C_AV_Config:I2C_blk|LUT_INDEX[1] was determined to be a clock but was found without an associated clock assignment.

新手 不懂,顶一下

你的那个信号应该是内部生成,又接到了内部模块的时钟脚上吧,quartus默认会把它看做时钟,你找到那个输出寄存器,然后设置Not A Clock就行了吧

要求要达到那么高,因为在400MHz下误差较小,所以才这样的,我的ENA模块貌似不是很完善,我贴出来给你看看哈同学说不要用initial语句,不用的话,因为我这里没有使能信号,所以不能不用吧。

////////This block is aimed at generating reset signal for the CLK_div10

////////and passing the original Trig to the output port

module ENA(clk1,clk2,trig,reset);

input clk1,clk2,trig;

output reset;

reg start;

reg [12:0] c;

assign reset = start;

initial begin

c <= 13'd0;

reset <= 0;

start <= 0;

end

///////////////////////////I THINK THIS ALWAYS IS NOT THAT GOOD

always @(posedge clk1)

begin//clk1(400MHz) as the beginner of the counter

if(trig)//once the trig is true,set the flag signal START becomes true.

start <= 1;

else

if(c==4096) start <= 0;//after the trig is being low and the number of the pulse(40MHz clk) is

end//big enough(we need at least 1024 pulses of output clk 40MHz),we reset

// the START signal to be false.

//////////////////////////////////////////////////////////

always @(posedge clk2)

begin//clk2(50MHz) as the trigger of the counter

case(start)

1:c <= c+1;//when the START signal is true,we start to count the counter

0:c <= 13'd0;//if start is low,which means we should stop generating 40MHz clk,

endcase// so we reset the counter

end

endmodule

但是我找不到你说的 Not A CLK?

- Quartus II 10.1可以直接导出原理图吗?急求大神解决(1970-01-01)

- 关于一个小警告的疑问(1970-01-01)

- 如何在nios ii IDE中写spi程序(1970-01-01)

- quartusII 11.0 器件库问题怎么解决(1970-01-01)

- 新手求助谁有关于NiosII的simple socket server模板的详解或资料?(1970-01-01)

- Quartus II 11.0 无法识别USB Blaster(1970-01-01)