xilinx官网中关于时序的讲解是不是错了

xilinx官网教材中ug612Timing Constraints,P120

其中DCM的输入是8ns(clk0)

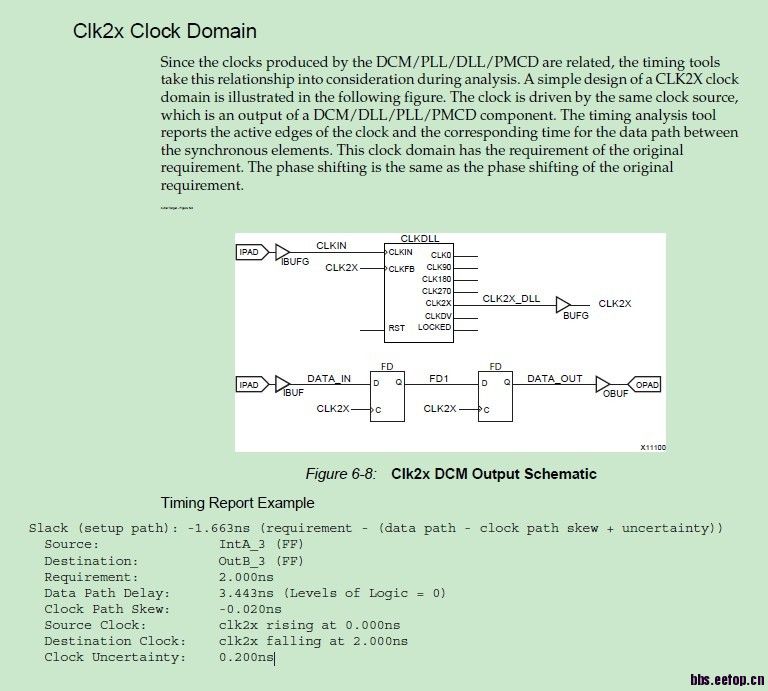

Slack (setup path): -1.663ns (requirement - (data path - clock path skew + uncertainty))

Source: IntA_3 (FF)

Destination: OutB_3 (FF)

Requirement: 2.000ns

Data Path Delay: 3.443ns (Levels of Logic = 0)

Clock Path Skew: -0.020ns

Source Clock: clk2x rising at 0.000ns

Destination Clock: clk2x falling at 2.000ns

Clock Uncertainty: 0.200ns

这句话中Destination Clock: clk2x falling at 2.000nsRequirement: 2.000ns

应该是Destination Clock: clk2x rising at 2.000ns,

Requirement: 4.000ns

可以这样理解吗?

因为下边的两个ffs是上升沿触发的,应该写成rising吧

期待XILINX专家给出权威解答,我也没看明白这个。

这个是最新版本的13.1的PDF,我看以往的pdf都也是这么写的,难道是图文不匹配吗?

看这个报告感觉你是约束了这个DCM的输入时钟,所以它告诉你,从这个DCM输出的时钟都被认为是相关时钟,并且按照相位频率关系生成了相关的约束。这个报告是没错的,rising 0.000是xilinx时序分析的起点,requirement应该是自动生成clk2x的period约束的周期值。所以时序分析工具就按照一个周期去分析你这条路径有没有问题。

IntA_3和OutB_3是两个FF,它分析的就是从IntA_3到OutB_3这条path的timing。 具体的,因为没有从你贴的图上看到这两个FF,所以你要找找看这两个FF在哪。可以告诉你的是,它分析的是IntA_3这个FF输出到OutB_3这个FF输入,这条路径上的组合逻辑的timing。不知道具体你这条路径是怎么设计的,但是这个3.433确实有点大了。

Destination Clock: clk2x falling at 2.000ns

为什么是falling呢,看图的话应该是rising 的,这两个触发器不是上升沿有效地吗?

还是这个时序说得压根不是上边的图呢

图上找不到IntA和OutB这两个FF啊。 如果单从这条报告来看,从rising到falling,那这个肯定是IntA用的是rising edge触发,OutB用的是falling edge触发。报告肯定不会错的。估计是跟上面的图不匹配。

图中的第二个reg应该是用clk2x的下降沿触发的,这样才讲的过去。

图中的第二个reg应该是用clk2x的下降沿触发的,这样才讲的过去。

- 为何时序仿真与功能仿真一致(已设置),没有延迟(1970-01-01)

- quartus ii 时序仿真出现了问题(1970-01-01)

- quartus用原理图描述后 功能仿真没有波形时序仿真波形正确(1970-01-01)

- Sigma-Delta MusicBox的速度优化(1970-01-01)

- 关于时序仿真到上板测试这段问题(1970-01-01)

- ISE Timing Anlayzer report(1970-01-01)