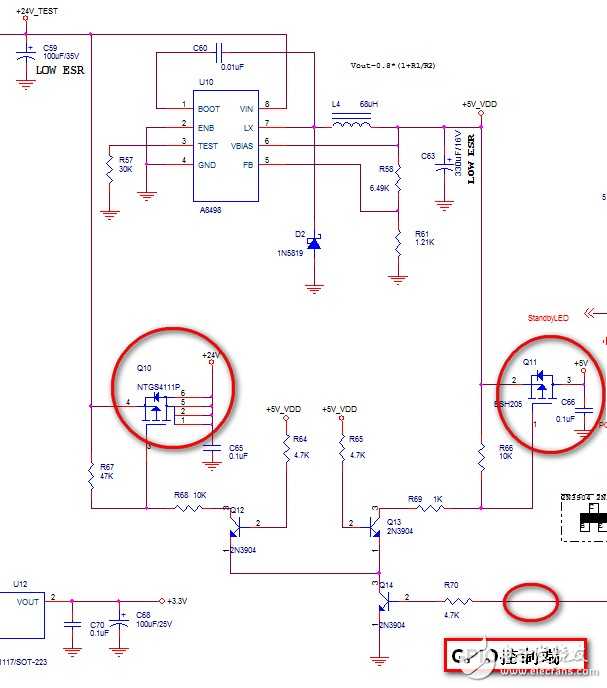

求解一个电源控制电路设计问题,谢谢!

工作时,其Q10/Q11Q都导通,给相关电源模块供电,待工作完成后,设计初衷是

通过GPIO口控制Q14三极管,来达到控制电源目的;

但是,现在的电路设计实际上是:Q11 的5V电压可控制,但Q10的24V没有达到设计目的,

不管,Q10的3PIN是高或低,其Q10端漏极都有24V电压输出!

请赐教,谢谢!

用5V去控制24V,建议加光耦隔离,直接用三极管控制 最容易出现这样的问题

1. 取消Q14,同时Q12和Q13的发射极接地;

2. GPIO控制端接到Q12和Q13的基极电阻。

谢谢发绕友宝贵的建议!增加光耦隔离可以解决,但是,我想明白我这样的设计,错误之处在哪?谢谢!

感谢你的提议,可以试试,理论看可行,但是我之前有确认,Q10的3PIN脚,不管是高还是低状态,其漏极都有输出。

刚实验跳线测试完毕,还是无法达到设目的,NG。谢谢!

测量下Q10和Q11的GS电压,看看是不是正常。

都正常(根据你的设计跳线测试),详细如下:1.GPIO口控制三极管导通时,其Q10,G端为低状态,输出端为:24V;Q11 G端为低状态,输出端为:5V;

2.GPIO口控制三极管截止时,其Q10,G端为高状态(24V),输出端为:24V;Q11 G端为高状态(5V),输出端为:0V;

感谢您的回复!

所以结论是,要么Q10管子坏了、要么管子极性错误……猜不出来是什么情况,除非给出GS电压的测量值(不是高电平或者低电平什么的)。

有确认过,Q10未损坏,且封装PIN脚OK;

GS两端的电压如下:

1.GPIO控制其三极管导通时,其GS两端电压为:-20V;

2.GPIO控制其三极管截止时,其GS两端电压为:0V;

Q10恐怕已经坏了,因为GS的击穿电压是±20V,而导通时电阻分压后的GS电压接近-20V……

实际上Q10的开启电压最多只要-3V就够了。搞个-5V~-6V就应该OK了。

注意P-MOS的导通条件,Vg-Vs<0 & |Vg-Vs|>Vth;因此建议你量一下GPIO为高和低的时候Q10 gate端的电压,如果是一直导通,调整R58试试

R68取值过大,关断时Q10的G对地也有4V的电压,这样就使得Q10过了门电压。你把R68换小一些

谢谢你的回复!这个问题我也考虑过,将R68改成1K/0603也是不行,谢谢!

漏极没有负载的情况下,会出现你说的现象