fpga/cpld数据采集与处理

时间:10-02

整理:3721RD

点击:

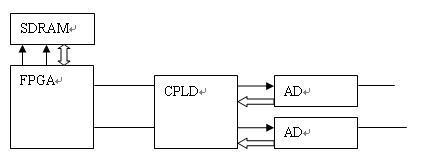

请大家考虑这么一个问题,如下图所示:

两路ad的输入为频率为1~1500hz的正弦波,此ad的性质为在输入时钟的上升沿时采集数据,在下一时钟周期的上升沿就可以利用此数据了。Ad的data有12位。Fpga与cpld 有20跟未定义管脚可以利用。

所做的事情是这样的,同时采集两路ad信号,把所采集的两路数据存放在sdram中再进行数字滤波等数字处理。由于fpga管脚不够,这里利用了cpld来扩展引脚。同时cpld来采集数据,而fpga来处理数据,形成流水线。Fpga的系统频率为50mhz,ad的最高转换速率为10mhz

一开始我的设想为:

Fpga与cpld有12为data连线,fpga往cpld送两位clk信号,一个为cpld_clk,一个位ad_clk.

这两路信号是经过系统频率适当的分频得出的,ad_clk与cpld_clk的周期相同,但ad_clk的占空比为1/2,cpld_clk的占空比为2/3.这样做的目的是在ad_clk的下一个上升沿来之前,利用cpld_clk的上升沿和下降沿分别读取ad1和ad2送来的12为数据。

这里模拟了一下

assign clk_ad1=clk_ad;

assign clk_ad2=clk_ad;

assign data[13:0]=count;

assign data[27:14]=count1;

always@(posedge clk_ad1)

begin

if(count==0)

begin

count<=14'b00001011110011;

end

else if(count==14'b11111111111111)

begin

count<=14'b00001011110011;

end

else

begin

count<=count+14'b00000000000001;

end

end

always@(posedge clk_ad2)

begin

if(count1==0)

begin

count1<=14'b00101010111100;

end

else if(count1==14'b11111111111111)

begin

count1<=14'b00101010111100;

end

else

begin

count1<=count1+14'b00000000000001;

end

end

always@(clk_cpld)

begin

if(clk_cpld==0)

begin

data_fpga=data[13:0];

end

else

begin

data_fpga=data[27:14];

end

end

endmodule

在fpga中加入DMA,readmaster为fpga与cpld相连的12为pio,即是data_fpga,

writemaster为sdram。Dma在sopc builder中的clk也为50mhz。

可最后sdram中的数据总是相同的,是不是由于dma传输速率为50mhz,而data_fpga数据跟不上,所以一直传输相同的数据啊。

如果是这样,有没有好的解决方案呢?

呵呵,大家帮帮考虑考虑!:))))))))

若有不明白的可联系53579621,或者留贴:))

两路ad的输入为频率为1~1500hz的正弦波,此ad的性质为在输入时钟的上升沿时采集数据,在下一时钟周期的上升沿就可以利用此数据了。Ad的data有12位。Fpga与cpld 有20跟未定义管脚可以利用。

所做的事情是这样的,同时采集两路ad信号,把所采集的两路数据存放在sdram中再进行数字滤波等数字处理。由于fpga管脚不够,这里利用了cpld来扩展引脚。同时cpld来采集数据,而fpga来处理数据,形成流水线。Fpga的系统频率为50mhz,ad的最高转换速率为10mhz

一开始我的设想为:

Fpga与cpld有12为data连线,fpga往cpld送两位clk信号,一个为cpld_clk,一个位ad_clk.

这两路信号是经过系统频率适当的分频得出的,ad_clk与cpld_clk的周期相同,但ad_clk的占空比为1/2,cpld_clk的占空比为2/3.这样做的目的是在ad_clk的下一个上升沿来之前,利用cpld_clk的上升沿和下降沿分别读取ad1和ad2送来的12为数据。

这里模拟了一下

assign clk_ad1=clk_ad;

assign clk_ad2=clk_ad;

assign data[13:0]=count;

assign data[27:14]=count1;

always@(posedge clk_ad1)

begin

if(count==0)

begin

count<=14'b00001011110011;

end

else if(count==14'b11111111111111)

begin

count<=14'b00001011110011;

end

else

begin

count<=count+14'b00000000000001;

end

end

always@(posedge clk_ad2)

begin

if(count1==0)

begin

count1<=14'b00101010111100;

end

else if(count1==14'b11111111111111)

begin

count1<=14'b00101010111100;

end

else

begin

count1<=count1+14'b00000000000001;

end

end

always@(clk_cpld)

begin

if(clk_cpld==0)

begin

data_fpga=data[13:0];

end

else

begin

data_fpga=data[27:14];

end

end

endmodule

在fpga中加入DMA,readmaster为fpga与cpld相连的12为pio,即是data_fpga,

writemaster为sdram。Dma在sopc builder中的clk也为50mhz。

可最后sdram中的数据总是相同的,是不是由于dma传输速率为50mhz,而data_fpga数据跟不上,所以一直传输相同的数据啊。

如果是这样,有没有好的解决方案呢?

呵呵,大家帮帮考虑考虑!:))))))))

若有不明白的可联系53579621,或者留贴:))

正在学习中,谢谢搂主

看看

看了一下,没有时间,没怎么弄明白,等有时间了再来

感觉lz这系统设计得真是。 :(

程序的风格需要改善

数据速率不匹配得地方需要匹配上

等这两个问题解决了再看会出什么问题。

ad_clk最好还是用50占空比得。

你得cpldclk 就是用来做了mux2 得控制端 控制 datafpga 从cnt0 和cnt1中选一个。

其实也没有必要这样啦。

如果你想对data做并串变换。

使用

assign datafpga:= (cpldclk)?data[13:0]: data[27:0];