实时数据采集系统,请教CPLD和FPGA高手

时间:10-02

整理:3721RD

点击:

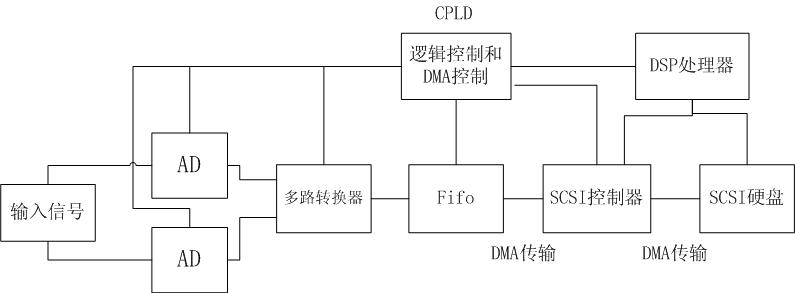

数据采集到后打算DMA传输,DMA控制器和其他时钟、时序等逻辑控制都由CPLD(或FPGA)来做,CPLD没有做过,所谓万事开头难嘛,请教高人,怎样对CPLD的功能做个总体规划和怎样入手,急哦,头催的紧,还请各位大哥大姐费心了

有想法就提出一点,对我都有用,小生先行谢过了

比如说有什么外围的东西(电源、晶振什么的)注意什么,要产生几个相关的时钟,是不是只能用一个时钟源,时钟改怎么产生,2个以上时钟频率相差很大怎么办,众多逻辑信号的延时怎么办,晕了

有想法就提出一点,对我都有用,小生先行谢过了

比如说有什么外围的东西(电源、晶振什么的)注意什么,要产生几个相关的时钟,是不是只能用一个时钟源,时钟改怎么产生,2个以上时钟频率相差很大怎么办,众多逻辑信号的延时怎么办,晕了

实时数据采集系统,请教CPLD和FPGA高手

up

一下

实时数据采集系统,请教CPLD和FPGA高手

最好用一个时钟源,否则存在不同时钟域交换数据的问题