面向微电子专业的免费培训--—工艺规则DRC/LVS/RCX的Rule开发及验证

微电子专业的本科生或者研究生就业时有一个困惑:虽然中国微电子领域对人才的需求缺口十分巨大,但是在高校所学的专业知识与用人单位的实际需求还是有一定差距。为弥补这这一短板,我们计划举办一个系列的免费专业课培训,该培训与普通培训的不同点在于:

1.从工业界的实际用例出发,由浅入深,把DRC/LVS/RCX Rule的开发与验证进行实用化、系统性的培训,而不是像传统的培训那样从学习语法的角度进行培训。

2.主讲教师在该领域具有10年左右的DRV/LVS/RCX核心算法开发经验,8年左右的工业界实际Runset应用开发经验,累计接近20年工业界经验,其领导开发的DRC Runset/LVS Rusnet/RCX Runset/Pcell的QA验证软件对工业界效率提升和准确性验证帮助很大。

3.理论与实际操作相结合,培训中更加注重实际操作,学生通过具体案例的操作将全面掌握该领域的知识与技能。

该培训对工程师和学生带来的直接好处是:

1.如果学生就业的方向是Foundry的研发岗位,目前国内Foundry在DRC/LVS/RCX Rule和PDK的开发方面急需该领域的人才,并且面向应届生广泛招聘。但是应届毕业生几乎没有该领域的经验,很难符合Foundry的应聘需求。经过本培训毕业的学生,可以很好地满足用人单位的专业需求,并且在动手能力和实际操作水平上超过用人单位的预期。

2.如果学生就业的方向是Fabless的设计公司,目前国内技术比较领先的IC设计公司对IC设计工程师的要求除了掌握基本的IC设计技能外,还要求对工艺规则有较好的掌握和理解,特别是当遇到工艺规则出现问题时,希望设计工程师可以分析和改进工艺问题。通过本培训,学生将掌握该领域的知识和技能,成为IC设计的复合型人才,未来在研发岗位可以发挥更大的作用,职业上升通道更有优势。

本次培训的内容有3个大的方向:

1.如何准确理解和把握工艺规则说明文档的文字和图示描述?

2.如何把上述文字和图示说明转换为DRC/LVS/RCX Rule的具体形式化描述?

3.如何验证DRC/LVS/RCX Rule的形式化描述符合工艺规则说明的原始需求?

培训大纲如下:

1.DRC Rule的开发和验证

a.基本规则Width, Spacing, Enclosure, Overlap的描述与开发

b.带有约束条件的规则描述与开发:Line End Spacing,Run LengthSpacing, Rectangle Enclosure, End ofLine Enclosure, Voltage Dependspacing,

Array Contact Spacing等。

c.天线效应规则(Antenna Rule)的描述与开发

d.与密度相关的规则(Density Rule)的描述与开发

e.复杂器件规则(Device Rule)的描述与开发

f.先进工艺带有FinFet,离散点规则的描述与开发

g.采用自动test pattern生成工具进行DRC Rule的验证

h.层次化(hierarchical)与扁平化(flatten)的比较

i.分析和优化DRC Rule的规则

j.主流DRC软件Calibre,PVS, ICV, Assura, Hercules工具的语法简介。

2.LVS Rule的开发和验证

a.工艺连接关系的建立

b.基本器件MOS, RES, DIO, CAP, BJT, VARACTOR, MIM的描述

c.识别层与器件Terminal的定义

e.器件属性Property的计算

f.WPE效应的计算

g.ERC的检查

h.LVSOption的含义

i.自动test pattern生成工具进行LVS Rule的检查

j.主流DRC软件Calibre,PVS,ICV,Assura,Hercules工具的语法简介。

3.RCX Rule的开发和验证

a.工艺纵向(Cross View)图的描述含义

b.如何把原始工艺纵向描述图转换为itf(mipt, ict)格式的文件?

c.如何把itf(mipt, ict)文件转换为StarRC, XCalibre, QRC的命令文件?

d.如何把StarRC, XCalibre, QRC的命令文件与LVS命令文件结合,提取寄生参数?

e.3维计算与2.5维计算的原理和应用

f.如何比较不同工具StarRC, XCalibre, QRC的精度?

g.自动test pattern生成工具进行RCX Rule的验证

4.Pcell QA的应用

a.自动把Pcell CDF数据包括最大值、最小值导入excel表格

b.自动比较不同版本的Pcell不同

c.自动比较Pcell参数与Spice Model的不同

d.自动对Pcell参数进行全面组合的LVS验证

e.自动对Pcell的连接关系和Terminal进行验证

f.自动对Pcell的Call Back函数进行验证

g.自动对Pcell进行hspice, spectre的前后仿真,比较与设计需求的误差

h.自动对Pcell进行ERC的验证

i.自动对Pcell进行全面组合的DRC验证

j.自动对参数设置进行分组管理,减少设置工作量

如有兴趣,可发私信联系。

DRC Code常犯错误举例

书写DRC Code时,由于疏忽导致流片失败的例子较多,常见的如下:

Gate露头检查的错误

规则描述:要求Gate的Poly图形必须伸出有源区0.18微米,如下图箭头g的图示:

下载 (43.15 KB)

下载 (43.15 KB)2 分钟前

规则中文字显式要求g的距离必须大于等于0.18微米,隐含的规则是(文字中没有说明):g不能等于0.0微米,即不能刚好touch在一起。许多开发工程师不理解隐含的规则,结果没有检查出刚好touch在一起的错误,导致流片失败!

ENCLOSURETOGT<0.18REGIONSINGULARABUT >0<90

上面Calibre Code中红色字体的选项ABUT >0<90没有检查出touch的错误,应该修改为: ABUT <90,就可以检查出露头的错误。

培训中将详细讲述如何通过自动工具发现该类错误并修改。

Nwell与Deep Nwell的距离检查的错误

规则描述:要求Nwell与Deep Nwell的距离不能小于3.5微米,如下图箭头e的图示,其中Nwell是图中TB的图形,DeepNwell是图中DN的图形:

下载 (115.31 KB)

下载 (115.31 KB)2 分钟前

规则中文字显式要求e的距离必须大于等于3.5微米,同时图示中有一个很重要的信息:Deep Nwell的图形位于Nwell图形的内部,而不是位于Nwell图形的外部,因此这个距离检查与普通的距离检查有本质的不同。普通的距离检查都是2个layer位于外部,而不是位于内部。许多开发工程师没有仔细看图示中的距离是外边对内边的距离,不是外边对外边的距离,结果没有检查出这种距离错误,导致流片失败!

EXTERNALTBDN <3.5MEASUREALLREGION

上面Calibre Code中红色字体的选项MEASURE ALL是用来检查外边对内边的距离的,由于工程师忘了写MEASURE ALL的选项,没有检查出该类错误。

培训中将详细讲述如何通过自动工具发现该类错误并修改。

下载 (65.79 KB)

下载 (65.79 KB)

8 分钟前

W2_c1其直接含义是:当Via2位于Metal1的线的Line End位置时,Metal1包围Via2的最小距离为0.05微米。

W2_c1的DRC Code书写

简洁的书写方法:

W2_c1 {

@W2_c1: Min extension of A1 beyond W2 must be >=0.05um (at least 2opposite sides)

X = ENC[W2]A1 < 0.05ABUT < 90OPPOSITE// 第一步

INTX<0.19ABUT==90INTERSECTING ONLY// 第二步

}

第一步图示解释:X 的结果为红色线段

下载 (100.32 KB)

下载 (100.32 KB)4 分钟前

第二步图示解释:输出报错的结果为红色线段

下载 (99.83 KB)

下载 (99.83 KB)4 分钟前

语法学习:

a.X= ENC ....,其含义是:把Enc的结果输出到X的变量中,但是并不输出到最终的报错结果中;没有赋值的变量才是DRC的最终报错结果。

b.[W2]的方括号含义是:把该命令输出的结果中与W2图形重合的边输出到X,不要把A1的的边也输出到X中。如果不写[ ],则默认把W2, A1的边都输出到X中。

c.INTERSECTING ONLY的含义是:把相互有交叉的边作为输出结果,不交叉的边不要做为输出结果。

d.INT < 0.19的含义是: W2的图形默认是0.19微米的方孔,工具输出时把0.19微米的边长都输出到结果中。如果写成0.18,则也会输出0.18错误结果,只是上图中的红色线段的长度只输出到0.18微米,剩余的0.01微米不显示报错了。

e.OPPOSITE的含义是:工具默认按照欧几里得距离输出结果,如果写了OPPOSITE的选项,则只输出2条对边相互有投影的部分。

寄生电容提取方法简介:

下载 (52.52 KB)

下载 (52.52 KB)

3 分钟前

下载 (114.18 KB)

下载 (114.18 KB)

3 分钟前

下载 (105.31 KB)

下载 (105.31 KB)

3 分钟前

下载 (60.29 KB)

下载 (60.29 KB)

3 分钟前

下载 (20.93 KB)

下载 (20.93 KB)

3 分钟前

下载 (41.65 KB)

下载 (41.65 KB)

1 分钟前

a1 - 副本.JPG (52.52 KB)

下载次数:0

3 分钟前

LVS 典型rule的定义:

下载 (111.84 KB)

下载 (111.84 KB)

40 秒前

Recognition Layer((Active OVERLAP Poly) AND NP) NOTNwell

Gate G((Active OVERLAP Poly) AND NP)NOT Nwell

Source S(((NP INTERACT Poly) NOT Poly) ANDActive) AND Nwell

Drain D(((NPINTERACT Poly) NOT Poly) AND Active) AND Nwell

多谢小编。

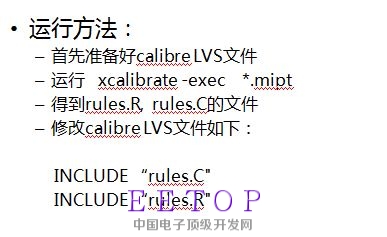

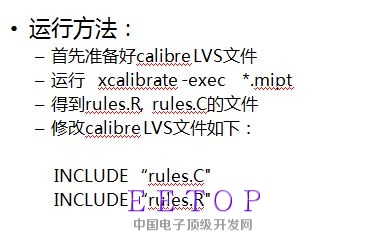

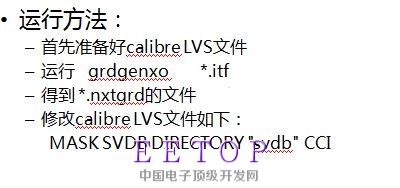

Calibre XRC Runset生成步骤:

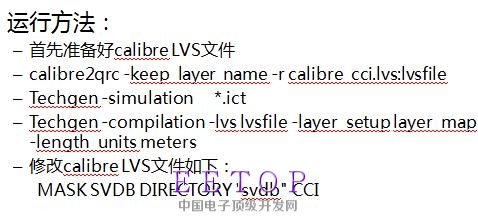

QRC Runset 生成步骤:

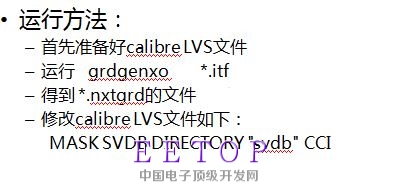

StarRC Runset生成步骤:

LVS Code要保证器件的Layer与工艺中定义的真值表完全一样,既不能

多写layer,也不能少写Layer。

下图真值表, 1表示must layer,必须有该layer, 0表示non layer,必须没有该layer, *表示任意。

TOGTSNSPTBVARMARKHVDNDN.markNA PA NH PH PWB VTSRAM.mark ESD SE VARMOS.mark EXT_SUB.mark

mn12111*0*0************

mp1211*11*0************

varlnmos111*110**********10

验证上述条件称之为Layer QA,可以自动化运行实现。

Layer QA的原理是:在器件图形的基础上,针对Must Layer,故意去掉该layer的图形,然后运行LVS,看结果是否不能提取出该器件,如果不能,则表示符合预期。同时,针对Non Layer ,在器件图形的基础上,故意添加一个该Layer的图形,然后运行LVS,如果能提取出器件,说明不符合预期。

自动运行显示结果如下:

======== qa_layer.log ========

qa_varlnmos_2t__bad_EXT_SUBINCORRECT

qa_varlnmos_2t__bad_HVCORRECT

varlnmos_2tCORRECT (+)

结果显示,Must Layer结果符合预期,而Non Layer中的EXT_SUB结果不符合预期,根据表达式,要求EXT_SUB layer必须不能在该器件中出现,结果显示即使添加了EXT_SUB layer,通过lvs提取后,也能把该器件提取出来,说明lvs code有问题。

打开lvs code,分析如下:

caplnGate=NOT OUTSIDE (((GT and ndiff) AND TB) NOT HV) VARMOS_mark

在上述语句中,HV图形通过NOT排除掉了,但是没有在该语句中加上NOT EXT_SUB的操作,如果加上该操作,则Layer QA就可以全部正确了。

根据现在报名的人数统计,我们初步计划先安排在上海的培训,上海的培训具体

时间还没有确定,初步安排在4月16日至4月20日这周。具体时间和地点一旦确定,

会及时通知。

其它地区的请先等待一下,后续会有通知。

针对上海地区的报名表已经通过email给感兴趣的人发送,有些没有留email地址的人请查收私信。

报名表请在4月13日前回复,过期不再等候。