H.264视频编解码纯FPGA低延迟解决方案演示DEMO

时间:03-15

整理:3721RD

点击:

点击以下文字观看H.264编解码demo.

H.264视频编解码低延迟解决方案配合自组网电台H.264视频编解码低延迟解决方案多路输入输出

H.264视频编解码FPGA解决方案原理讲解

H.264视频编解码FPGA解决方案DEMO

西安银亿电子科技有限公司基于多年的技术沉淀和工程化应用,提出该解决方案。该解决方案是全部代码自主研发,使用FPGA为核心器件,实现H.264编解码的IP核。此解决方案为纯硬件的解决方案,启动时间可以忽略,编解码延迟为固定的延迟,在一定的优化情况下,可以最大限度提升图像的压缩比。

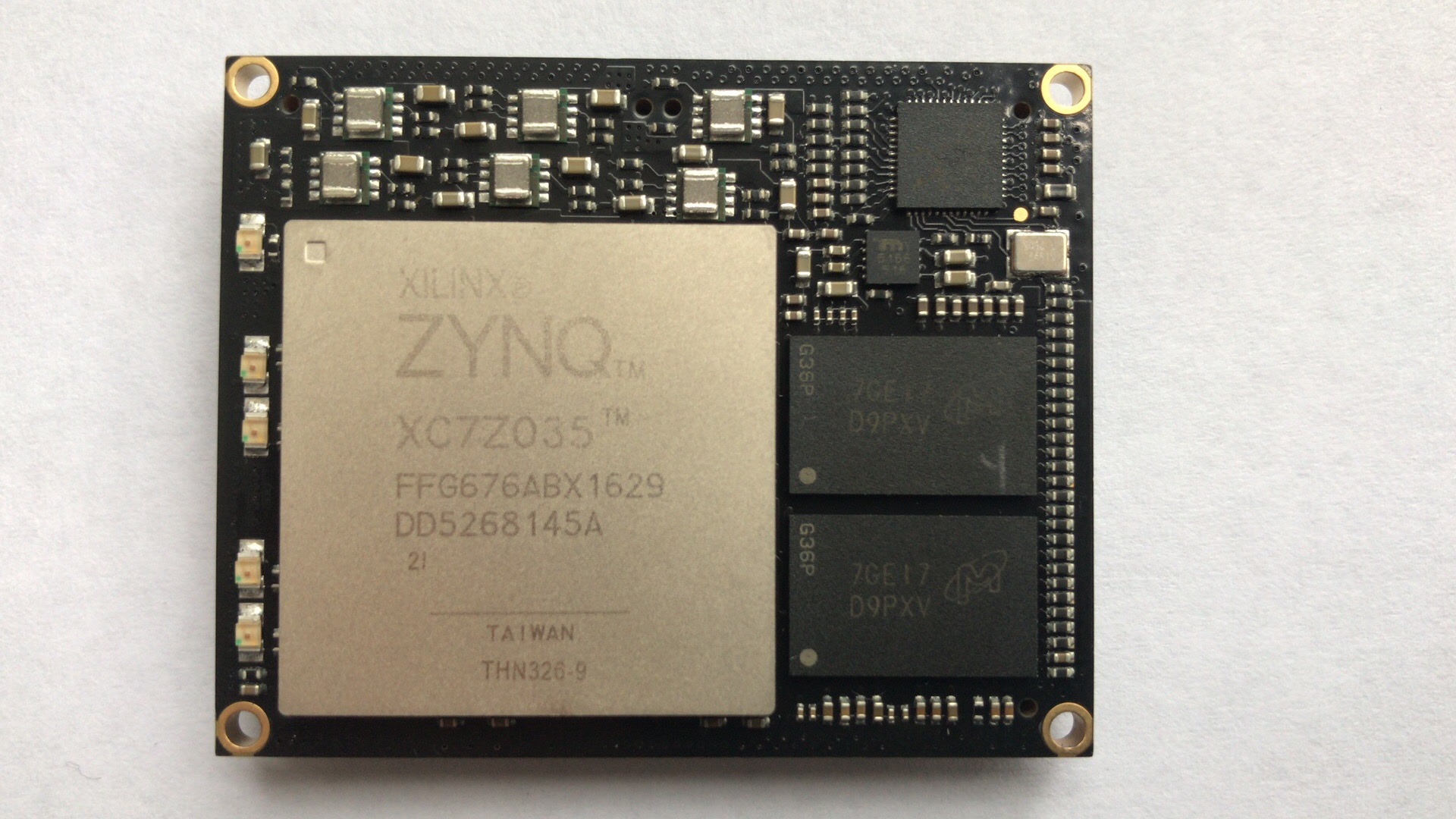

该H264_Lite视频编解码器(encoder&decoder),其由硬件描述语言verilog实现,此设计经过FPGA EDA工具编译后可集成于可编程逻辑器件(FPGA)平台;也可以使用Synopsys Design Compiler综合后作为asic芯片的IP核使用。该视频编码器输出码流完全符合H.264视频编码标准;解码器能解码H264_Lite自己编码的码流。 该设计针对硬件面积,编码帧率,综合频率做了设计结构上的优化。 该设计对FPGA实现做了特别的时序优化,例如,在Xilinx Zynq7020上可以单核就能够实现1080P@60fps的FPGA应用场景,双核可以实现4K@30fps以上的应用场景。

2.具体特点

1)支持各种分辨率

单core最大支持的分辨率为4K;视频分辨率配置灵活,支持各种非标分辨率,如1024*1024等;可通过多个core的并行处理,支持4K*2K、4K*4K等超高分辨率。可支持多路不同分辨率视频输入,编解码后输出。

2)支持各种帧率

单core最大可支持4K/30fps,1080P/120fps。可根据硬件资源和客户需求提供帧率定制,如960P/120fps等。

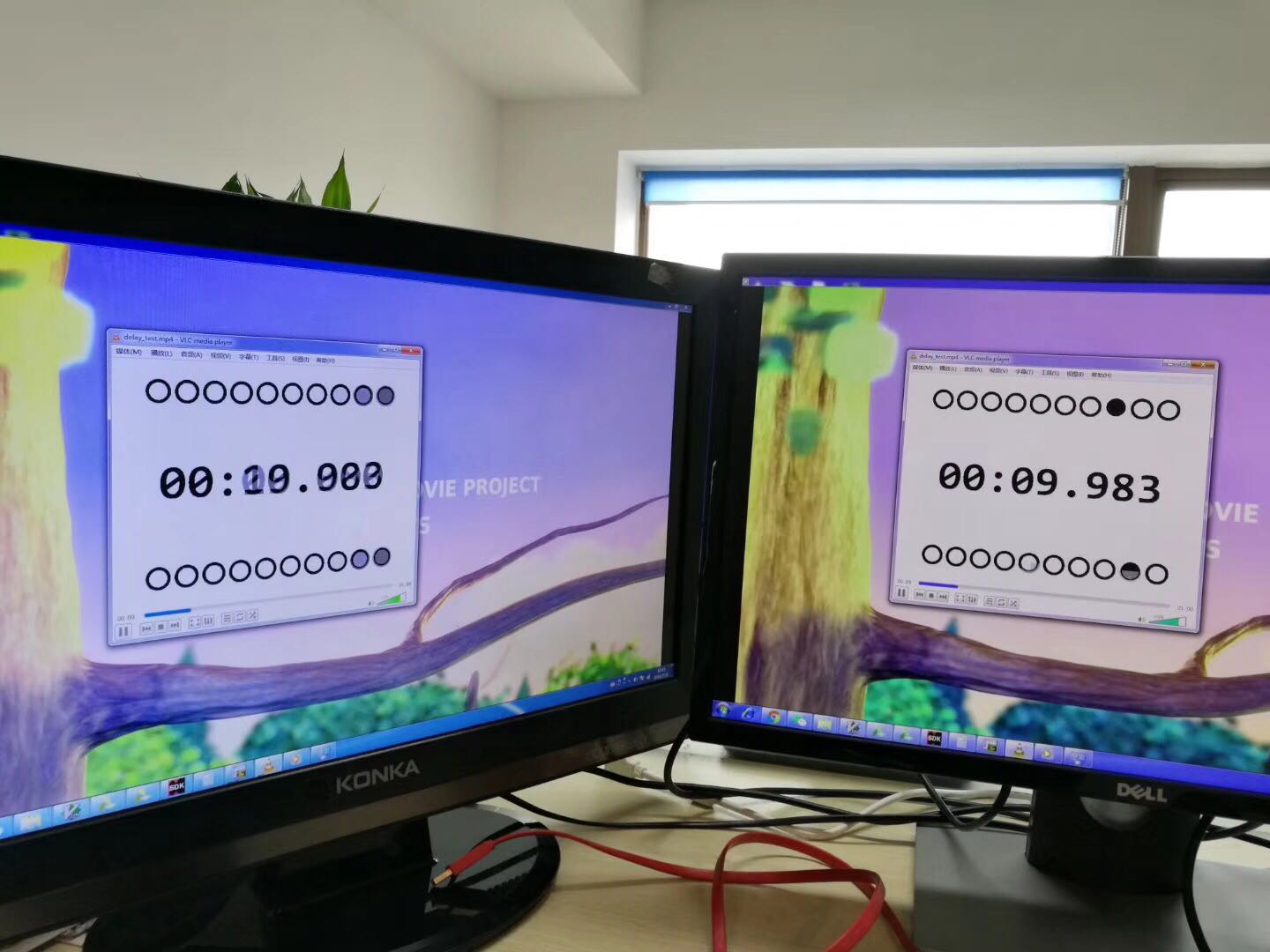

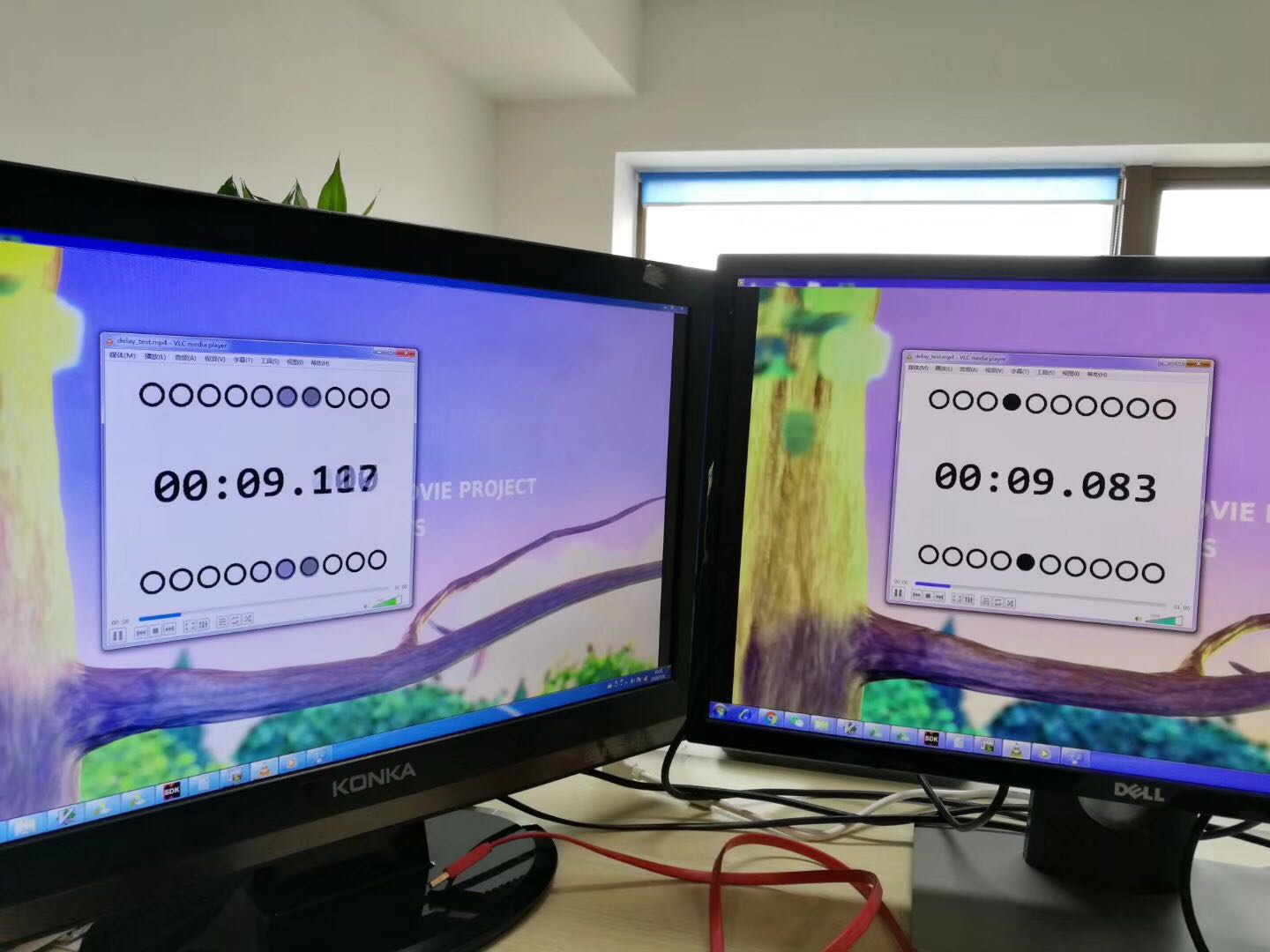

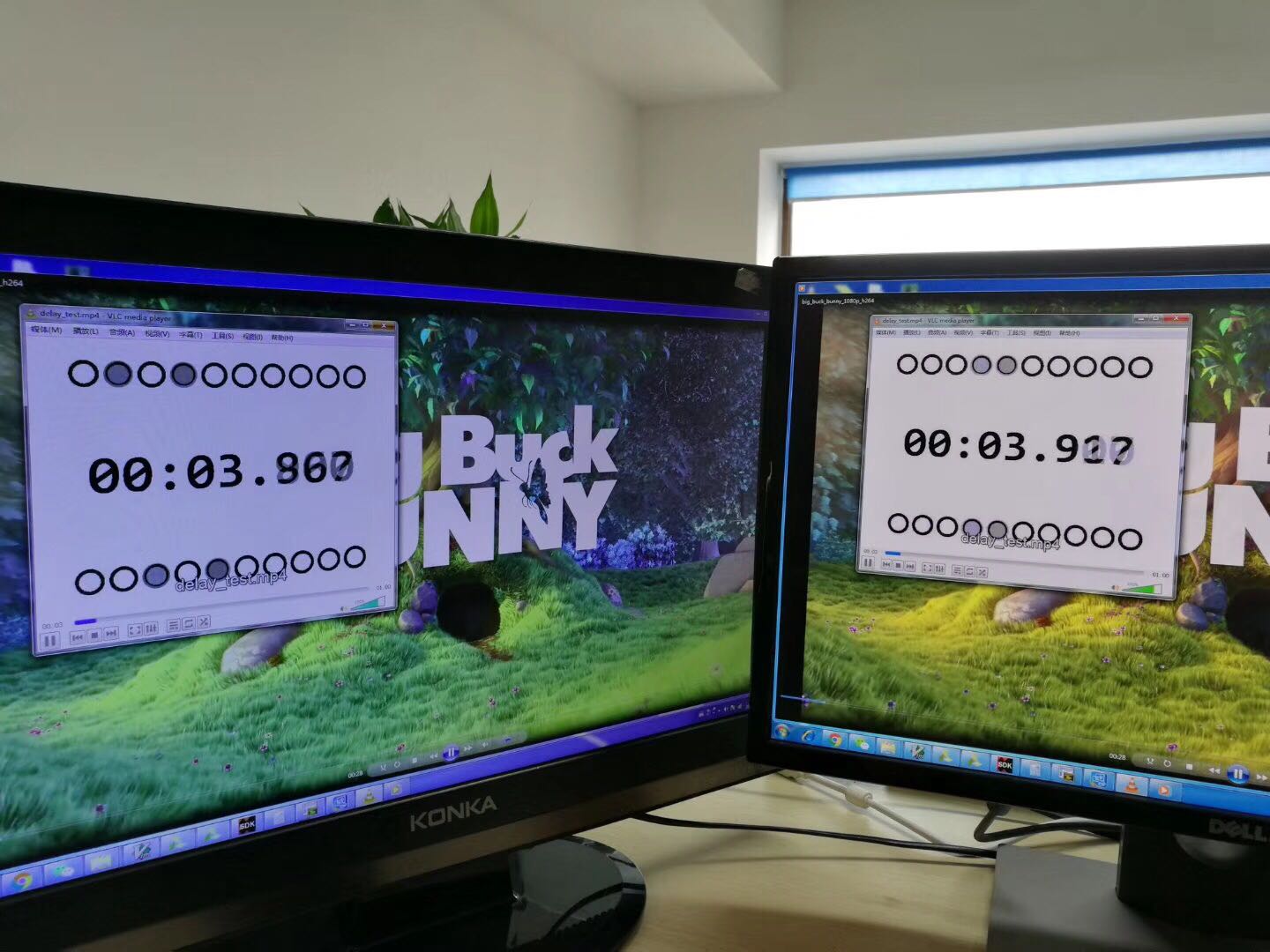

3)编解码延迟低

编码的延迟低至0.5ms左右,解码的延迟15ms以下,由编码,传输码流,到解码,所组成的完整系统中,延时在30-60ms左右;特殊应用场景解码延时可进一步优化至10ms以下。

4)占用FPGA资源小

单core所占的资源中,LUT占用最多,约为29000多个,其他的资源在占用率方面,均比LUT占比小。例如,在zynq7020上,只占55%的逻辑资源,硬件功耗超低。

5)码率控制灵活

带宽受限时,可以通过动态调整QP值(图像质量),将码流控制在要求的带宽之下。在带宽足够时,可以稳定QP值(图像质量),以达到较好的图像质量要求。

6)超长GOP支持

最大可以256帧才编码一个I frame,削减码流带宽高峰,仍保持优秀的容错性。

7)定制性强

可根据实际需求优化代码,提供例如局部QP(图像质量)增强等定制化的修改。

8)可移植性强

在保证硬件资源的情况下,可支持不同厂家的FPGA,兼容性、可移植性超强。

9)应用领域

低带宽下、超低延时的星载/机载/弹载/车载视频数据链;

需要超高清晰度、超低延时的摄像监控系统;

海量视频数据压缩、存储等。

连个主页都没有吗?呵呵。

准备用xilinx的mpsoc

什么主页?官网吗?

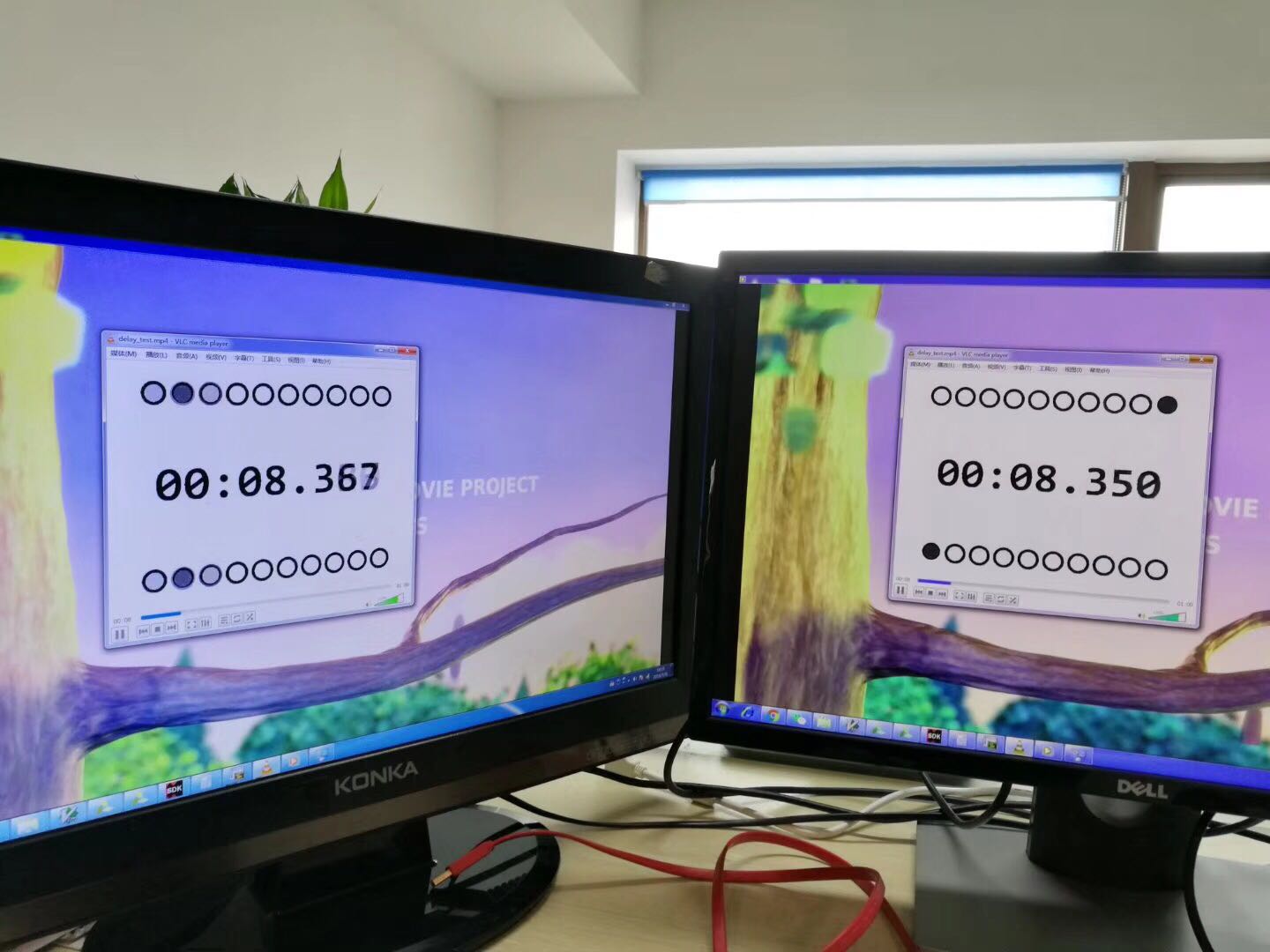

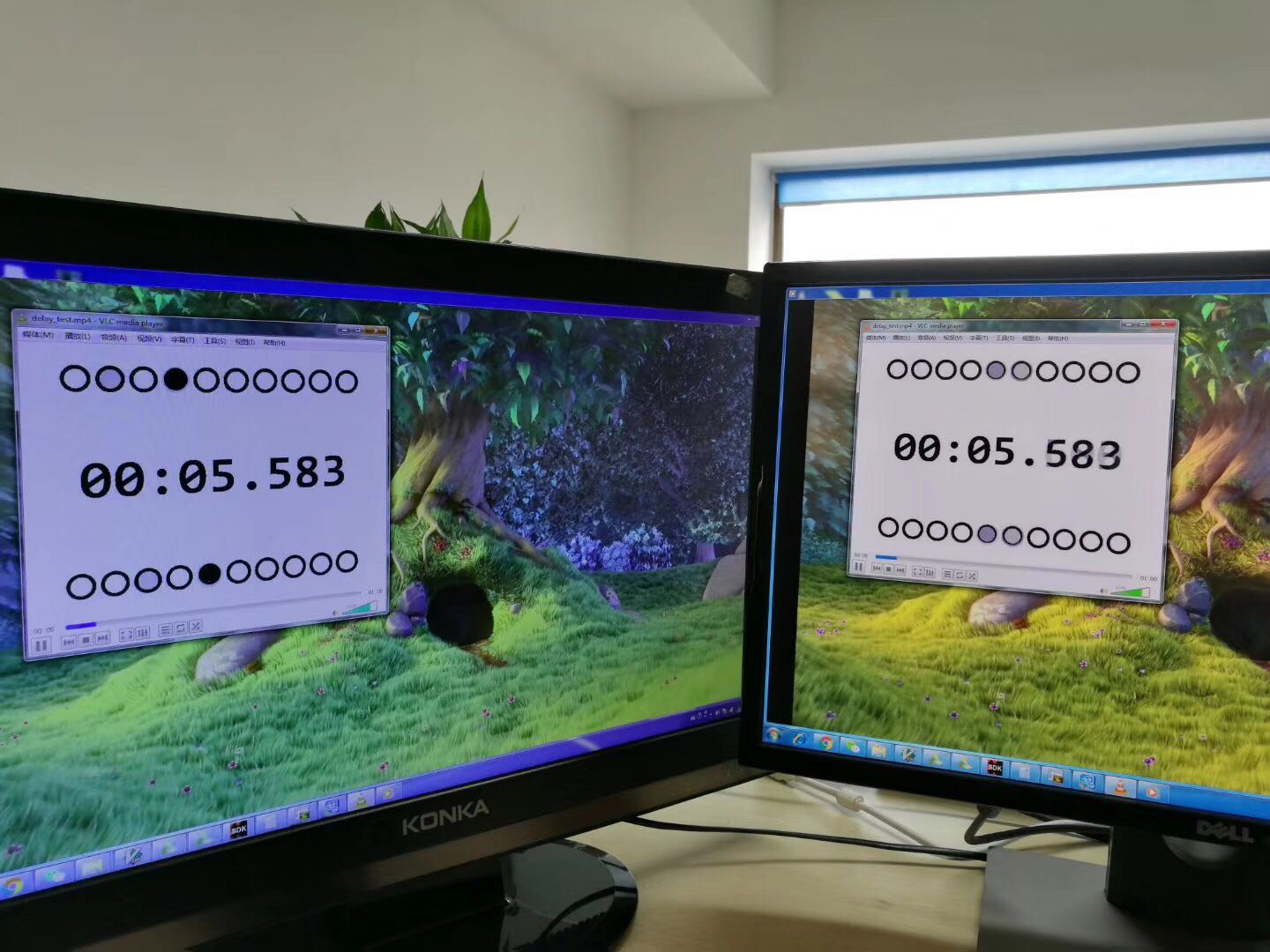

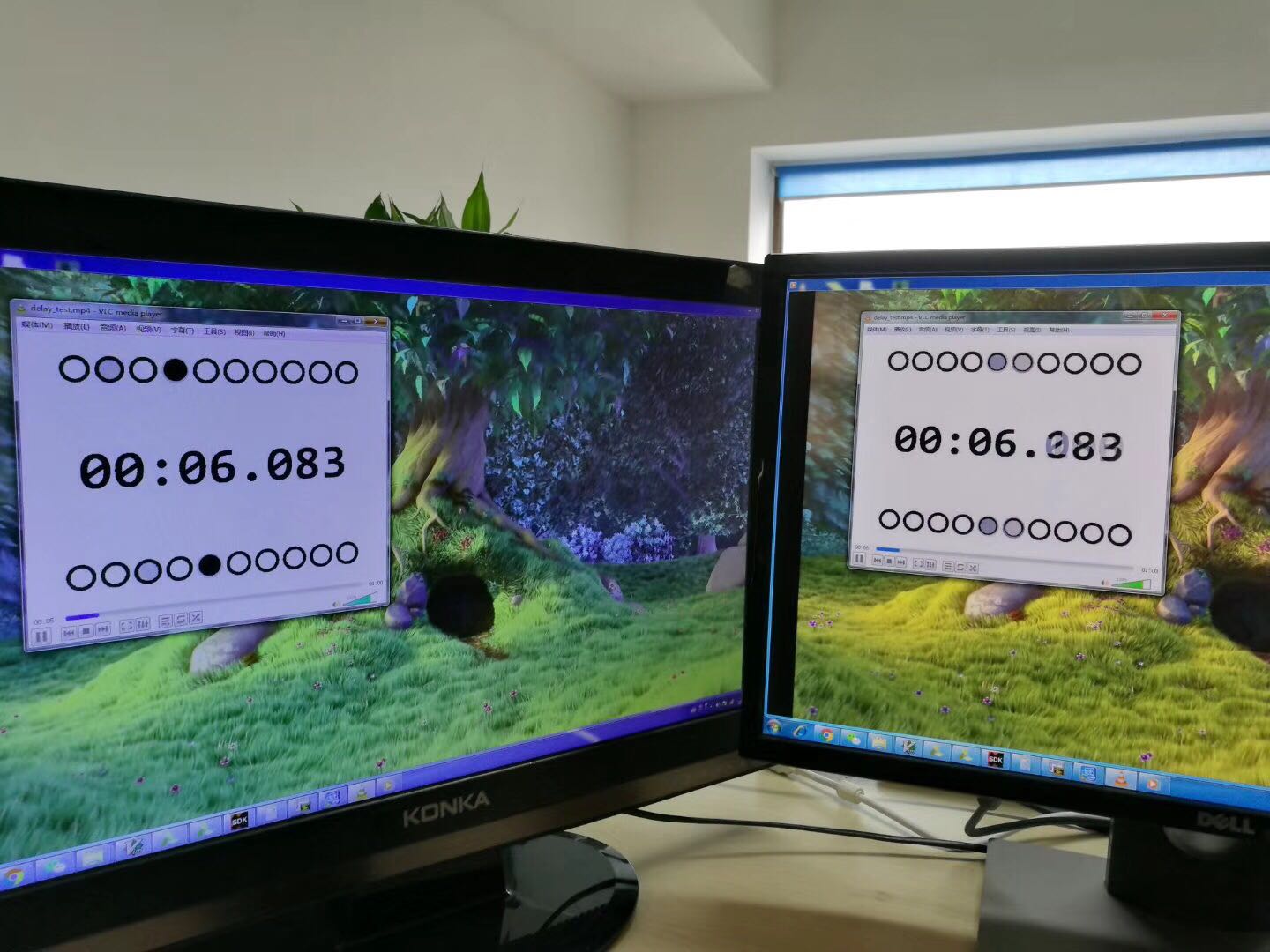

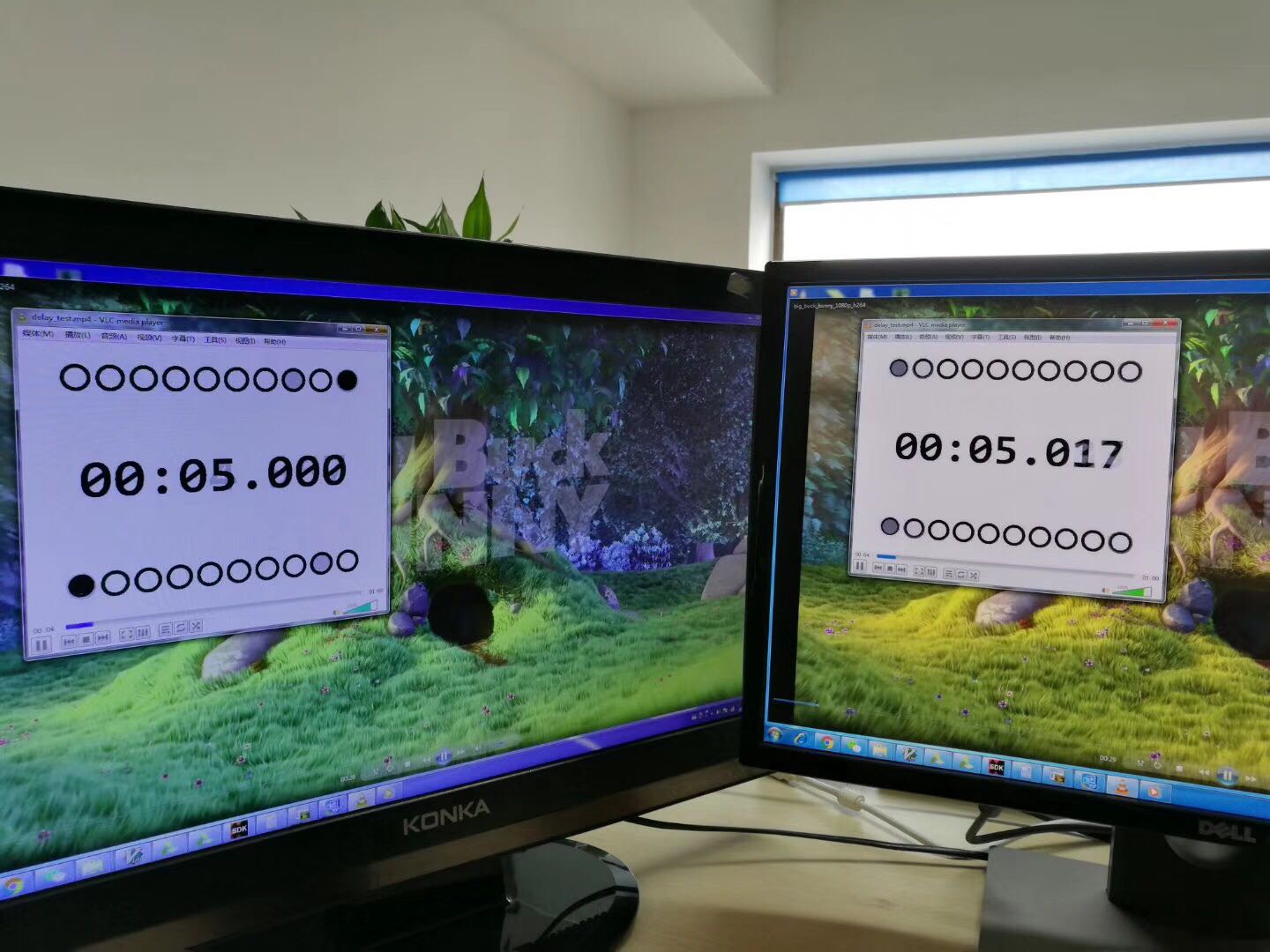

1080P30帧,图像采集+编码+解码+显示,系统总延时在0ms~33ms之间(看配图)。

谢谢小编!

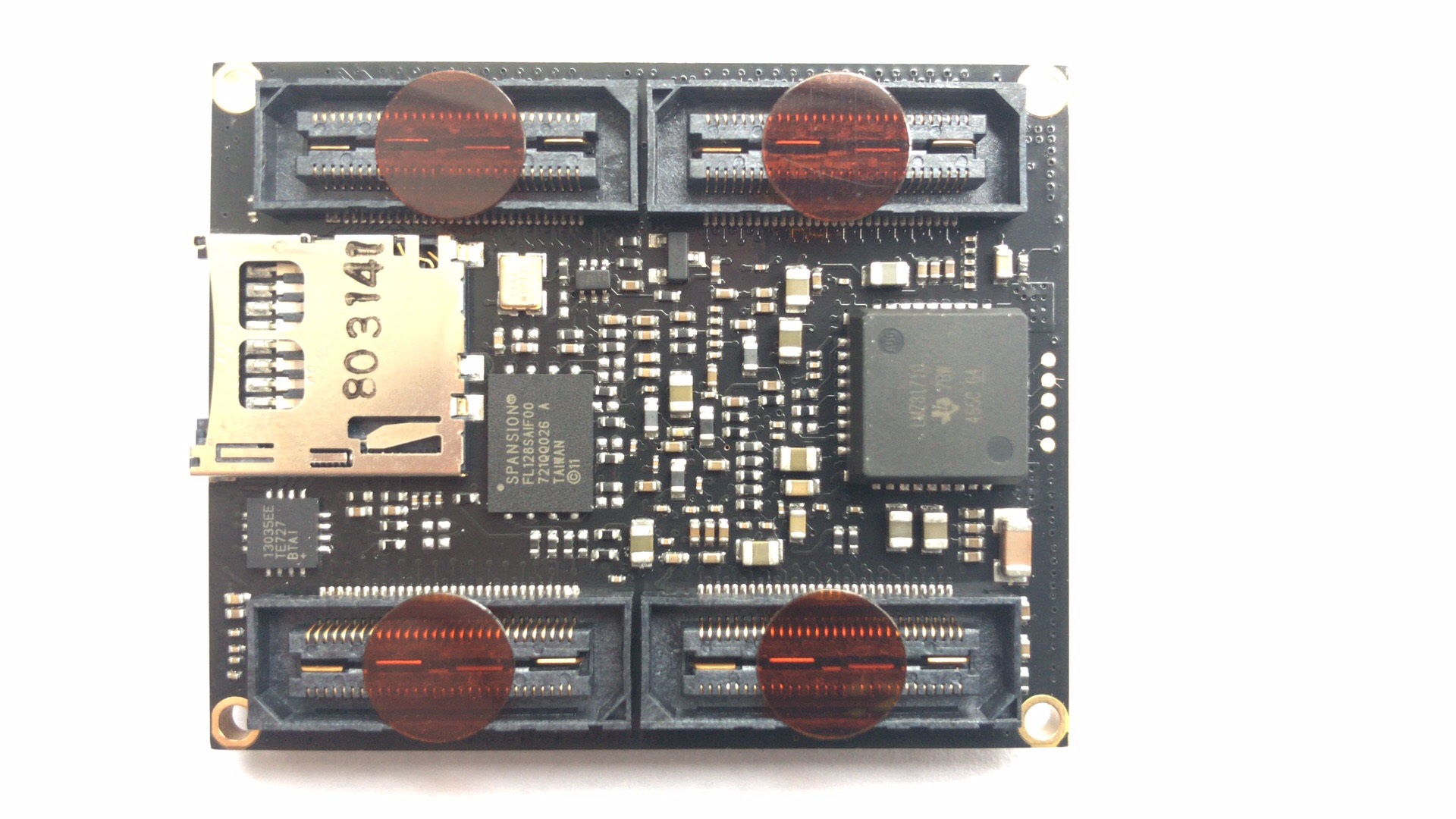

ZYNQ 7035小系统(40mm*50mm),网口/串口/jtag/tf卡一应俱全!