求助 VHDL代码中的synopsys translate off和synopsys translate on之间的作用

时间:03-15

整理:3721RD

点击:

求帮助

下面代码中synopsys translate off和synopsys translate on之间的代码有什么作用 如果把这段代码去掉 对结果有什么影响啊

--synopsys translate off

IF NoX /= '0' THEN

NoX := '1';

ELSE

NoX := '0';

END IF;

--synopsys translate on

不让工具综合。

VHDL也有综合吗?综合具体指什么呀,呵呵 我知道的比较少,

如果把这段代码去掉的话,对结果有影响吗

具体怎么写啊?我试了,结果语法错误

前面是

--synopsys tranlate off

这个-- 是什么啊

首先明白:编译器指示语句

有时,可以利用HDL描述中的一些特定的注释语句来控制综合工具的工作,从而弥补仿真环境和综合环境之间的差异,这些注释语句称为编译器指示语句(Compiler Directives)。

Verilog编译器指示语句

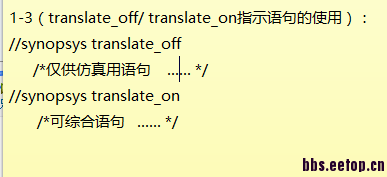

1) translate_off/ translate_on

这组语句用来指示DC停止翻译 “//synopsys translate_off”之后的Verilog描述,直至出现 “//synopsys translate_on”。当Verilog代码钟含有供仿真用的不可综合语句时,这项功能能使代码方便地在仿真工具与综合工具之间移植。

一些代码竟被识别为“危险字符”,不能发表回复

掌握学习了,谢谢

?