DC综合时报错 Clock clr used as data

题目:设计一个简易异步接收机,用BCD05工艺库实现(从代码到版图)。

1M==1us

1.接收机功能

发送机等价为一个11位的移位寄存器,发送数据时以固定的125KHz的频率移位。发送数据格式见图1。发送机在空闲状态下(不发送数据时)txd端口(与接收机的rxd相连)为1,由于发送数据的第一位总是0,故接收机可检测到一个“负跳变”以实现发送与接收的同步。接下来的8位是要求接收的数据,接收机应能够正确接收该数据,使接收端的b[7:0]等于发送端的b[7:0]。发送端的第10位为奇偶校验位e,e等于b0^b1^b2^b3^b4^b5^b6^b7,接收机可根据接收到的b[7:0]与e的关系判断是否发生了数据传输错误。发送数据的最后一位为固定的1,确保空闲状态下txd端口为1。

2.接收机端口定义

(1)rxd:接收数据端口

(2)rst_n: 同步复位端,低有效。

(3)rcv_en:接收使能信号,高有效。

(4)b[7:0]: 接收数据。

(5)rcv_ok: 接收正确的标志。每次接收开始时清0,接收到校验位e后,根据运算决定输出,1表示正确,0表示错误。

(6)rcv_st:接收状态。1表示正在接收过程中,b[7:0]不可用,0表示已完成接收,b[7:0]可用。

3.设计环境

(1)所有输出端负载为0.1PF。

(2)所有输入信号内阻为1k。

(3)所有输入信号上升、下降时间不超过2ns。

(4)rcv_en端输入延迟为时钟周期的20%。

(5)输出延迟为时钟周期的30%。

4.答题要求

(1)设计代码

(2)验证代码,包括正确的和有接收错误的。

(4)状态机和数据通道图。

(5)仿真结果

(6)逻辑综合脚本

(7)版图

尝试了修改latch 块,但改完功能受影响;

求助各位大神,怎么解决而影响功能呀

我写的verilog代码如下:

//2014-06-22

module tg(b,a,y);

input a;

input b;

output y;

reg y;

always@(a or b)

if(a==1'b1)

y=b;

else

y=1'b1;

endmodule

//----------------------------------------------------------------------------------------------------------------

module det(din,clk,rst_n,en,neg);

input din;

input clk;

input rst_n;

input en;

output neg;

reg q1;

reg q2;

reg neg;

always @(posedge clk)

begin

q1<=din;

q2<=q1 ;

if(rst_n==1'b0 )

neg<=0;

else if(en==1'b0 && din==1'b0)

neg<=q1^q2;

else

neg<=0;

end

endmodule

//---------------------------------------------------------------------------------------------------------

module latch(clk,clr,y);

input clk;

input clr;

output y;

//--------------------

reg y;

reg x;

//--------------------

always@(negedge clr)

if(clr==1'b0)

y<=1'b0;

//------------------------

always@(clk)

begin

x=1'b1;

if(clk==1'b1)

y=x;

end

endmodule

//-----------------------------------------------------------------------------------------------------------

module dff(data,clk,clr,q);

input data;

input clk;

input clr;

output q;

reg q;

always@(posedge clk or posedge clr )

if(clr==1'b1)

q<=1'b0;

else

q<=data;

endmodule

//-------------------------------------------------------------------------------------------------------

module cnt16(clk,clr,ena,co);

input clk;

input clr;

input ena;

output co;

reg co;

reg [3:0]q;

always@(posedge clk or negedge clr)

begin

if(clr==1'b0)

q<=4'h0;

else if(ena==1'b1)

if (q==4'b1111)

q<=4'b0000;

else q<=q+1'b1;

end

always@(q)

begin

if(q==4'b1111)

co=4'h1;

else

co=4'h0;

end

endmodule

//--------------------------------------------------------------------------------------------------------

module cnt11(clk,clr,ena,q,co);

input clk;

input clr;

input ena;

output [3:0]q;

output co;

reg [3:0]q;

reg co;

always@(posedge clk or negedge clr)

begin

if(clr==1'b0)

q<=4'h0;

else if(ena==1'b1)

if (q==4'b1010)

q<=4'b0000;

else q<=q+1'b1;

end

always@(q)

begin

if(q==4'b1010)

co=4'h1;

else

co=4'h0;

end

endmodule

//-----------------------------------------------------------------------------------------------------------

module receiver_fsm(clk,rst_n,x1,neg,rcv_st,q1,q2);

input clk;

input rst_n;

input [3:0] x1;

input neg;

output rcv_st;

output q1;

output q2;

//---------------

reg rcv_st;

reg q1;

reg q2;

reg [2:0]cs;

reg [2:0]ns;

//---------------------

parameter idle =3'b000;

parameter st1=3'b001;

parameter st2=3'b010;

parameter st3=3'b011;

parameter st4=3'b100;

parameter st5=3'b101;

//---------------------

always@(posedge clk)

if(rst_n==1'b0)

cs <=idle;

else

cs <=ns;

//---------------------------------------

always@(cs or x1 or neg)

case(cs)

idle:

begin

{rcv_st,q1,q2}=3'b000;

if(x1==4'b0000)

ns=st1;

end

st1:

begin

{rcv_st,q1,q2}=3'b001;

if(x1==4'b0000)

ns=st1;

else if(4'b0001<=x1<=4'b0111)

ns=st2;

end

st2:

begin

{rcv_st,q1,q2}=3'b101;

if(x1==4'b1000)

ns=st3;

end

st3:

begin

{rcv_st,q1,q2}=3'b100;

if(x1==4'b1001)

ns=st4;

end

st4:

begin

{rcv_st,q1,q2}=3'b110;

if(x1==4'b1010)

ns=st5;

end

st5:

begin

{rcv_st,q1,q2}=3'b010;

if(neg==1'b1)

ns=idle;

end

endcase

endmodule

//-----------------------------------------------------------------------------------------------

module s2p (sdata,clk,rst_n,en1,en2,in1,out,pdata);

output [7:0] pdata;

output out;

input sdata,clk,rst_n,en1;

input en2,in1;

reg out;

reg [7:0] pdata;

reg [7:0] p_reg;

//---------------------------------------

always @(posedge clk or negedge rst_n)

if (rst_n==1'b0)

begin

pdata <=8'h00;

end

else if(en1==1)

begin

pdata[7:0]<=8'hzz;

p_reg[7:1]<=p_reg [6:0];

p_reg[0]<=sdata;

end

else if(en1==1'b0)

begin

pdata<=p_reg;

end

//----------------------------------------------

always@(en2 or in1 or p_reg)

if(en2==1'b0)

out=1'b0;

else

out=in1^~yh(p_reg);

functionyh;

input[7:0] a;

integer i;

begin

yh=a[0];

for (i=1;i<8;i=i+1)

begin

yh=yh^a;

end

end

endfunction

//--------------------------------------

endmodule

//------------------------------------------------------------------------------------------------------

module receiver2(rxd,rst_n,rcv_en,clk,b8bit,rcv_ok,rcv_st);

input rxd;

input rst_n;

input rcv_en;

input clk;

output [7:0] b8bit;

output rcv_ok;

output rcv_st;

//---------------------------

wire s0,s1,s2,s3,s4,s5,s7,s8,s10;

wire [3:0]s6;

reg [2:0]cs,ns;

//-----------------------------

parameter idle=3'b000;

parameter st1=3'b001;

parameter st2=3'b010;

parameter st3=3'b011;

parameter st4=3'b100;

//----------------------------

tg u1(.b(rcv_st),.a(rcv_en),.y(s0));

det u2(.din(rxd),.clk(clk),.rst_n(rst_n),.en(s0),.neg(s1));

latch u3(.clk(s1),.clr(s2),.y(s3));

latch u3_1(.clk(s10),.clr(s1),.y(rcv_ok));

dff u4(.data(rxd),.clk(s4),.clr(s1),.q(s5));

cnt16 u5(.clk(clk),.clr(rst_n),.ena(s3),.co(s4));

cnt11 u6(.clk(s4),.clr(rst_n),.ena(s3),.q(s6),.co(s2));

receiver_fsm u7(.clk(clk),.rst_n(rst_n),.x1(s6),.neg(s1),.rcv_st(rcv_st),.q1(s8),.q2(s7));

s2p u9(.sdata(rxd),.clk(s4),.rst_n(rst_n),.en1(s7),.en2(s8),.in1(s5),.out(s10),.pdata(b8bit));

//---------------------------------------------------------------------------------------------------------

endmodule

测试代码如下

module receiver2_tb();reg rxd;reg rst_n;reg rcv_en;reg clk;wire [7:0] b8bit;wire rcv_ok;wire rcv_st;//-----------------------------receiver2 u0(.rxd(rxd),.rst_n(rst_n),.rcv_en(rcv_en),.clk(clk),.b8bit(b8bit),.rcv_ok(rcv_ok),.rcv_st(rcv_st));//-----------------------task half_pulse;inout clock;#2.5clock = ~ clock;endtask//----------------------------------------------------------------------------task pulse;input[31:0] num;integer i;for(i=0;i<num;i=i+1)beginhalf_pulse(clk);half_pulse(clk);endendtask//-------------------------------initial beginrst_n=1'b0;rcv_en=1'b1;clk=1'b0;rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;rst_n=1'b1;#95rxd=1'b0;//begin bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b0;//e bit#95rxd=1'b1;//end bit#95 rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;//12 bite 1#95rxd=1'b0;//begin bit#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;//e bit#95rxd=1'b1;//end bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;//12 bite 1#95rxd=1'b0;//begin bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b0;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;//e bit#95rxd=1'b1;//end bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;//12 bite 1#95rxd=1'b0;//begin bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;//e bit#95rxd=1'b1;//end bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;//12 bite 1#95rxd=1'b0;//begin bit#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b0;#95rxd=1'b0;#95rxd=1'b1;#95rxd=1'b1;#95rxd=1'b1;//e bit#95rxd=1'b1;//end bitend//--------------------initial pulse(50000000);//-----------------------endmodule

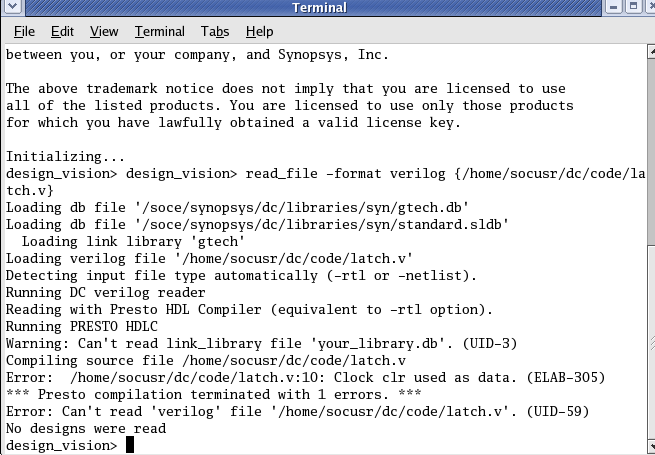

用DC编译时报错如下图

脚本文件如下

#------------------------------------------------------------------------------# File: A TCL format DC script file # Author : xinxn # date: 2010-08-04#------------------------------------------------------------------------------set TECH_LIB_PATH"/iclibs/CSMCBCD05/synopsys"set SYMBOL_LIB_PATH "/iclibs/CSMCBCD05/icons"set CORE_LIB"IC05CScore_50_typbcdv10.db"set IO_LIB"IC05CSpad_50_typbcdv10.db"#------------------------------------------------------------------------------set search_path [concat $TECH_LIB_PATH $search_path]set search_path [concat $SYMBOL_LIB_PATH $search_path]echo $search_path#------------------------------------------------------------------------------set target_library {IC05CScore_50_typbcdv10.db}set link_library {* IC05CScore_50_typbcdv10.db IC05CSpad_50_typbcdv10.db}set symbol_library {IC05CScore.sdb}#------------------------------------------------------------------------------# add DesignWare Libs to link library#------------------------------------------------------------------------------set SYN_LIB {dw_foundation.sldb}lappend link_library $SYN_LIB#------------------------------------------------------------------------------#------------------------------------------------------------------------------set WORK_DIR /home/socusr/dcset THIS_DESIGN receiver2#------------------------------------------------------------------------------# reports path and file#------------------------------------------------------------------------------set SETUP_RPT_FILE $WORK_DIR/report/setup_time.rptset HOLD_RPT_FILE$WORK_DIR/report/hold_time.rptset AREA_RPT_FILE$WORK_DIR/report/area.rptset CELL_RPT_FILE$WORK_DIR/report/cell.rptset POWER_RPT_FILE $WORK_DIR/report/power.rptset VIOL_FILE$WORK_DIR/report/voilation.rpt#----------------------------------------------------------------------------------set NETLIST_FILE$WORK_DIR/netlist/receiver2_gate.vset SDC_FILE$WORK_DIR/sdc/receiver2.sdc#----------------------------------------------------------------------------------set CLK_PER 5set IN_DLY [expr $CLK_PER * 0.2]set OUT_DLY [expr $CLK_PER * 0.3]set MAX_TRANSITION 0.1#----------------------------------------------------------------------------------read_verilog $WORK_DIR/code/receiver2.vcurrent_design $THIS_DESIGNlinkcheck_design#----------------------------------------------------------------------------------set ALL_EX_CLK [remove_from_collection [all_inputs] [get_ports clk]]#----------------------------------------------------------------------------------# design rules constrAInts#----------------------------------------------------------------------------------# set driving ability of input ports and load of output ports.#----------------------------------------------------------------------------------set_drive 1.0 $ALL_EX_CLKset_drive 0 [get_ports clk]set_load0.1 [all_outputs]#----------------------------------------------------------------------------------set auto_wire_load_selection trueset_max_transition $MAX_TRANSITION $THIS_DESIGNset_max_fanout 6 $ALL_EX_CLKset_max_fanout 2 [get_ports rst_n] #-----------------------------------------------------------------------------------# Timing constraints#-----------------------------------------------------------------------------------create_clock -p $CLK_PER -name CLK [get_ports clk]set_clock_latency 1.0 [get_clocks CLK]set_clock_uncertainty -setup 0.1 CLKset_clock_uncertainty -hold 0.1 CLKset_input_delay -max $IN_DLY -clock CLK $ALL_EX_CLK set_input_delay -min 0.5 -clock CLK $ALL_EX_CLKset_output_delay $OUT_DLY [all_outputs]#-----------------------------------------------------------------------------------report_port #-----------------------------------------------------------------------------------set_dont_touch_network [get_clocks CLK]uniquifyset_max_area 0compile -map_effort high#-----------------------------------------------------------------------------------report_constraint -all_violators > $VIOL_FILE#-----------------------------------------------------------------------------------report_timing > $SETUP_RPT_FILEreport_timing -delay min > $HOLD_RPT_FILE#-----------------------------------------------------------------------------------report_cell>$CELL_RPT_FILEreport_area>$AREA_RPT_FILEreport_power >$POWER_RPT_FILE#-----------------------------------------------------------------------------------#-----------------------------------------------------------------------------------write -format verilog -hier -o $NETLIST_FILEwrite_sdc -nosplit $SDC_FILE#quit

尝试了修改latch 块,但改完功能受影响;

求助各位大神,怎么解决而影响功能呀