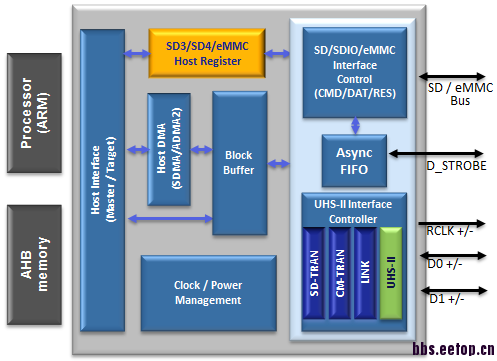

eMMC 5.1 host controller

时间:03-15

整理:3721RD

点击:

*Compliance

.Compliant with eMMC Specification Version 5.1

.AMBA AXI Specification Version 3.00 (Standard)

.AMBA AHB Specification Version 2.00 (Optional)

.OCP specification Version 2.2 (Optional)

*Core Features

.Supports one of the following System/Host Interfaces: AHB, AXI or OCP

.Data transfer using PIO mode on the Host Bus Slave interface, using DMA mode on the Host Bus Master interface. Here the Host Bus is AHB or AXI or OCP Interface

.Supports eMMC5.1 Security Protocol Commands

.Supports 32-bit and 64-bit system bus

.Configurable FIFO size to support different block sizes

.Supports Interrupts and wake up functionality

.Supports Internal Clock divider for various card operational modes

*eMMC 5.1 features

.Host clock rate variable between 0 and 200 MHz

.HS400 high speed interface timing mode of up to 400 MB/s data rate

.Field firmware update

.eMMC device health report

.eMMC production state awareness

.Secure removal types

.Backward compatible to 1-bit, 4-bit and 8-bit modes

.Supports Primary & alternate boot modes

.Supports Packed commands, Data Tags, Discard & Sanitize features

.Supports 4KB block support

.Supports Tuning for HS200 mode

.Cyclic Redundancy Check CRC7 for command and CRC16 for data integrity

.Supports MMC Plus and MMC Mobile

.Password protection of Cards

:(:(:(

你好,你的回复是ip吗

:(:(

感谢小编的分享

thanks