verilog语言求纠错

module BCD_cnt59(qout,cin,reset,clk);

output[7:0] qout;

reg[7:0]qout;

input cin,clk,reset;

always@(posedge clk )

begin

if(reset)

qout<=0;

else if(cin)

begin

if(qout[3:0]==4'd0)

begin

qout[3:0]<=9;

if(qout[7:4]==0)

qout[7:4]<=5;

else

qout[7:4]=qout[7:4]-1'b1;

end

else qout[3:0]<=qout[3:0]-1'b1;

end

end

endmodule

module BCD(in,out);

output[6:0]out;

input[3:0]in;

reg[6:0]out;

always@(in)

begin

case(in)

4'd0ut=7'b1111110;

4'd1ut=7'b0110000;

4'd2ut=7'b1101101;

4'd3:out=7'b1111001;

4'd4:out=7'b0110011;

4'd5:out=7'b1011011;

4'd6:out=7'b1011111;

4'd7:out=7'b1110000;

4'd8:out=7'b1111111;

4'd9:out=7'b1111011;

default:out=7'bx;

endcase

end

endmodule

module top (out1,out2,clk,reset,cin);

output[6:0] out1,out2;

input clk,reset,cin;

wire [7:0] qout;

BCD_cnt59 u1(qout,cin,clk,reset);

BCD u2 (qout[7:4],out2);

BCD u3 (qout[3:0],out1);

endmodule

高人给看看呗

module BCD_cnt59(qout,cin,reset,clk);

output[7:0] qout;

reg[7:0]qout;

input cin,clk,reset;

always@(posedge clk )

begin

if(reset)

qout[3:0]<=4'b0;

else if(cin)

begin

if(qout[3:0]==4'd0)

qout[3:0]<=9;

else

qout[3:0]<=qout[3:0]-1'b1;

end

end

always@(posedge clk )

begin

if(reset)

qout[7:4]<=4'b0;

else if(cin)

begin

if(qout[7:4]==4'd0)

qout[7:4]<=4'd5;

else

qout[7:4]<=qout[7:4]-1'b1;

end

end

endmodue

估计这才是你想表达的吧,你那个太复杂了,你说是波形问题,我就改了代码的内容而不是形式

我直接在这儿写的你自己debug 一下.下面一个模块很清晰

好的,谢谢你。我试一下

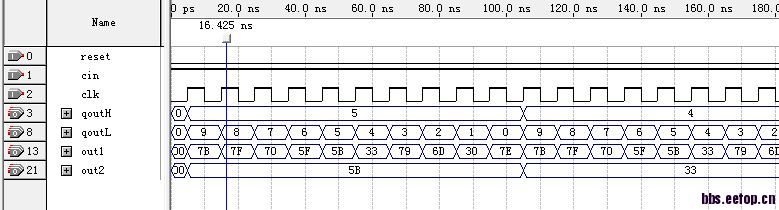

你是不是想要这样的结果?(我按照我自己的习惯改了很多,qoutH,qoutL,也不用output)

module top (out1,out2,qoutH,qoutL,clk,reset,cin);

output[6:0] out1,out2;

reg[6:0] out1,out2;

input clk,reset,cin;

output[3:0] qoutH,qoutL;

reg [3:0] qoutH,qoutL;

always @(posedge clk)

begin

if(reset)begin qoutH=4'h0;qoutL=4'h0;end

else if(cin)

begin

if(qoutL==4'h0)

begin

qoutL[3:0]=4'h9;

if(qoutH==4'h0) qoutH=4'h5;

else qoutH=qoutH-1;

end

else qoutL=qoutL-1;

end

BCD(out2,qoutH);

BCD(out1,qoutL);

end

task BCD;

output[6:0] out;

input[3:0]in;

begin

case(in)

4'h0ut=7'b1111110;

4'h1ut=7'b0110000;

4'h2ut=7'b1101101;

4'h3:out=7'b1111001;

4'h4:out=7'b0110011;

4'h5:out=7'b1011011;

4'h6:out=7'b1011111;

4'h7:out=7'b1110000;

4'h8:out=7'b1111111;

4'h9:out=7'b1111011;

default:out=7'hx;

endcase

end

endtask

endmodule

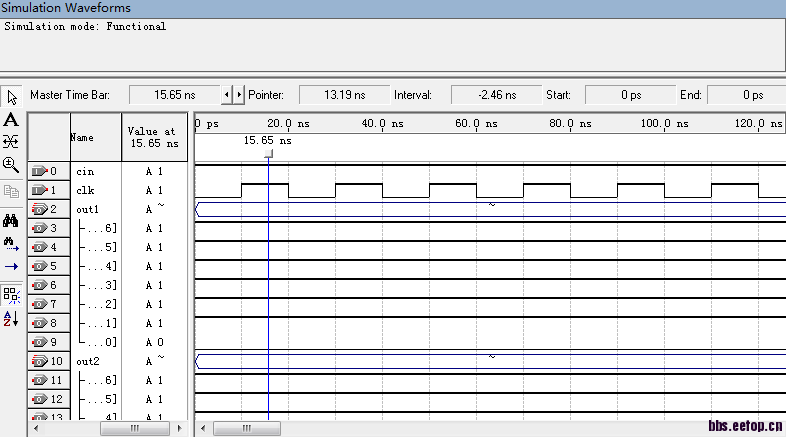

你检查 一下自己的reset 信号,波形上没有啊

你是调用的时候 reset clk 弄反了

module top (out1,

out2,

clk,

reset,

cin);

output[6:0] out1,out2;

input clk,reset,cin;

wire [7:0] qout;

BCD_cnt59 u1(qout,cin,clk,reset);

BCD u2 (qout[7:4],out2);

BCD u3 (qout[3:0],out1);

endmodule

module BCD_cnt59(qout,

cin,

clk,

reset);

output[7:0] qout;

input cin;

inputclk;

inputreset;

reg[7:0]qout;

always@(posedge clk )

begin

if(reset)

qout[3:0]<=4'b0;

else if(cin)

begin

if(qout[3:0]==4'd0)

qout[3:0]<=9;

else

qout[3:0]<=qout[3:0]-1'b1;

end

end

always@(posedge clk )

begin

if(reset)

qout[7:4]<=4'b0;

else if(cin)

begin

if(qout[7:4]==4'd0)

qout[7:4]<=4'd5;

else

qout[7:4]<=qout[7:4]-1'b1;

end

end

endmodule

module BCD(in,

out);

output[6:0]out;

input[3:0]in;

reg[6:0]out;

always@(in)

begin

case(in)

4'd0ut=7'b1111110;

4'd1ut=7'b0110000;

4'd2ut=7'b1101101;

4'd3:out=7'b1111001;

4'd4:out=7'b0110011;

4'd5:out=7'b1011011;

4'd6:out=7'b1011111;

4'd7:out=7'b1110000;

4'd8:out=7'b1111111;

4'd9:out=7'b1111011;

default:out=7'bx;

endcase

end

endmodule

谢谢你!确实是这个问题。另外你的程序里也有些错误,我想做的是59到0的计时器,你的程序没有表达出各位变成0之后十位再改变这个意思吧?

另外,我想在加一个20MHz--1HZ的分频器在这个模块中,程序我已经写好,如下

module time1Hz(clk1Hz, clk_20M);

input clk_20M;

output clk1Hz;

reg[24:0] temp_count;

initial

temp_count <= 25'b0;

always @ (posedge clk_20M)

if (temp_count == 25'b1_0011_0001_0010_1101_0000_0000)

temp_count <= 25'b0;

else

temp_count <= temp_count + 1;

assign clk1Hz = temp_count[25];

endmodule

问题是怎么用顶层调用模块来调用它呢?顶层调用模块该怎么写?求指点!