求问为什么在使用chipscope的时候时钟连不上?

时间:11-27

整理:3721RD

点击:

最近在尝试使用chipscope对波形信号进行抓取,然后在网上找来点资料来看,有2个方法实现。 使用 IP Core Generator的时候,抓取波形没问题,可以通过chipscope看到信号。

但是如果使用chipscope Inserter的时候,就不行了。完全触发不了。

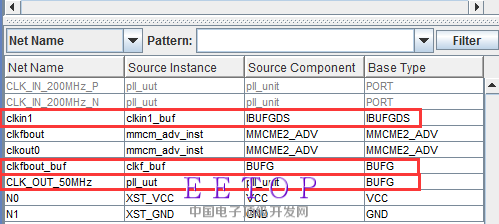

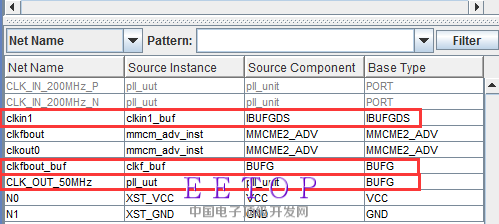

于是我怀疑是不是在使用chipscope Inserter的时钟没有把时钟连接好,我使用的是Virtex-7,使用了差分信号输入(V-7貌似没有全局时钟输入,于是选择了差分信号的系统时钟。)在chipscope的时序时钟和v文件的时钟连接时,应该选择哪个时钟?我把下图中的时钟都连接了一篇(那个clk-out是PLL的输出时钟),波形还是没触发(一直是0)

所以我是哪里出错了吗? 我用Core Generator在代码中例化后,使用chipscope是可以看到波形的。

但是如果使用chipscope Inserter的时候,就不行了。完全触发不了。

于是我怀疑是不是在使用chipscope Inserter的时钟没有把时钟连接好,我使用的是Virtex-7,使用了差分信号输入(V-7貌似没有全局时钟输入,于是选择了差分信号的系统时钟。)在chipscope的时序时钟和v文件的时钟连接时,应该选择哪个时钟?我把下图中的时钟都连接了一篇(那个clk-out是PLL的输出时钟),波形还是没触发(一直是0)

所以我是哪里出错了吗? 我用Core Generator在代码中例化后,使用chipscope是可以看到波形的。

FPGA ASIC quartus Xilinx vivado verilog ALTERA CPLD 集成电路 相关文章:

- 旧版本生成的 DDR2 IP ,新版本的 MegaWizard 打不开。(1970-01-01)

- 写一段HDL代码实现对输入时钟三分频的功能(1970-01-01)

- FPGA多时钟设计(1970-01-01)

- 为什么FPGA时钟频率不高,却适合做高速处理?(1970-01-01)

- FPGA Verilog HDL 设计实例系列连载------交通灯的控制(1970-01-01)

- 基于VHDL的FPGA与NIOS_II实例精炼视频教程免费下载(1970-01-01)

栏目分类

最新文章