关于generate,ODDR,OBUFDS 数据传输问题

时间:11-27

整理:3721RD

点击:

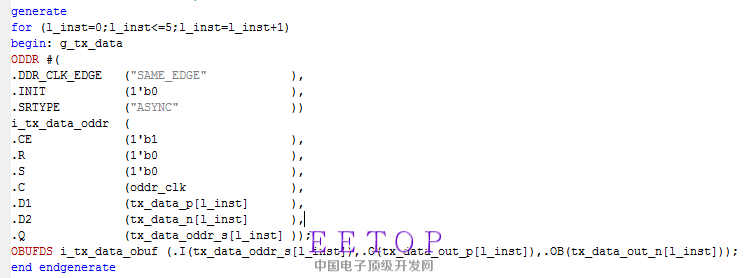

请问最后实现的是tx_data_p[l_inst] 到tx_data_out_p[l_inst];

tx_data_n[l_inst] 到tx_data_out_n[l_inst] 吗?

查了一下V7 spec,好像不是这样。

ODDR的作用:

每个cycle采样tx_data_p & tx_data_n,转换成双倍速率从Q输出,

输出格式的序列:D1.D2.D1.D2.D1.D2...以此类推(注意,double rate)

OBUFDS作用:

将一个信号转换成差分输出,我个人理解是O = I, OB = ~I;

所以,输出应该是:

tx_data_out_p 序列:tx_data_p(cycle1), tx_data_n(cycle1), tx_data_p(cycle2), tx_data_n(cycle2)...

tx_data_out_n 序列:跟tx_data_out 相反。

若有大神路过,错误请指正。

简单仿真了一下,就是如此。

建议小编也仿真仿真,一看波形就明白了。

是的,我仿真了一下,是如你所说的这样。谢谢!但是还有一个问题就是在这个程序里OBUFDS出来的两路作为AD9361的输入端,按理说tx_data_out_p作为I路,tx_data_out_n作为Q路,然后进行DA转换输出。那为什么tx_data_out_p要同时携带tx_data_p和tx_data_n的信息。做这个ODDR的意义在于什么呢?

不知道您做过相关的工作么?

FPGA ASIC quartus Xilinx vivado verilog ALTERA CPLD 集成电路 相关文章:

- 旧版本生成的 DDR2 IP ,新版本的 MegaWizard 打不开。(1970-01-01)

- 写一段HDL代码实现对输入时钟三分频的功能(1970-01-01)

- FPGA多时钟设计(1970-01-01)

- 为什么FPGA时钟频率不高,却适合做高速处理?(1970-01-01)

- FPGA Verilog HDL 设计实例系列连载------交通灯的控制(1970-01-01)

- 基于VHDL的FPGA与NIOS_II实例精炼视频教程免费下载(1970-01-01)

栏目分类

最新文章