使用LabVIEW的FPGA模块实现传感器信号的采集问题

时间:10-02

整理:3721RD

点击:

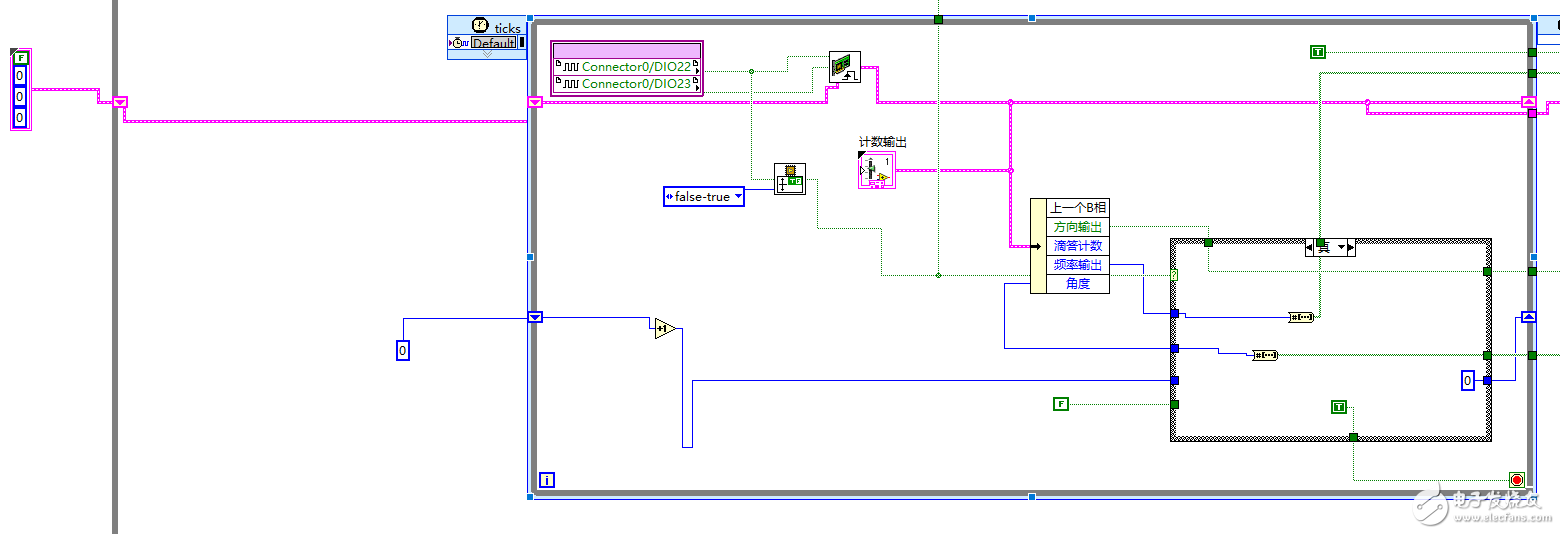

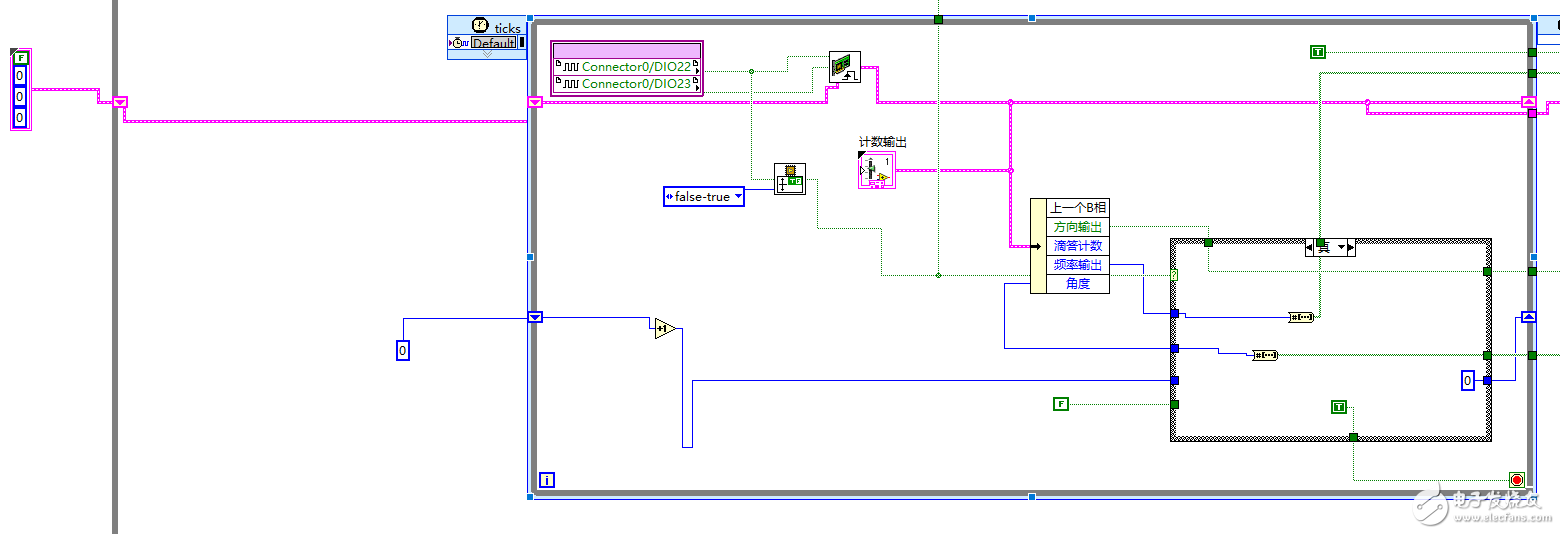

这个传感器信号采集系统中有两个采集对象,分别为传感器A和传感器B,希望实现的效果为,在传感器A的上升沿信号到来时,同时进行对传感器B的数据的读取,然后将两者的数据写入FIFO输出到上位机程序。

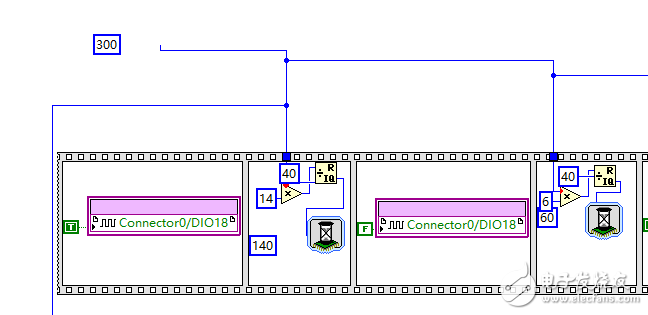

现在我通过设置一个时钟为40MHZ的定时循环读取DIO22 / DIO23 即传感器A的A相和B相信号,通过布尔相交判断其上升沿,每两个上升沿之间进行计数,并在新的上升沿到来时退出该循环。

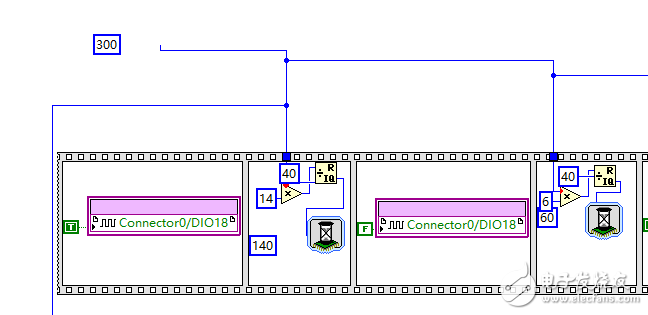

而读取传感器B的信号是根据时序图配置芯片的引脚电平来实现的,因此添加了平铺式顺序结构,设置了一定的延时留时间给芯片进行配置。

而读取传感器B的信号是根据时序图配置芯片的引脚电平来实现的,因此添加了平铺式顺序结构,设置了一定的延时留时间给芯片进行配置。

上述两个部分均在一个大的while循环中,每执行完一遍以上的程序,就重新开始一次循环。

现在的问题是,当传感器A的信号频率上升到100KHz以上时,计时循环的输出值出现了错误,在同一个周期下计数值呈现规律性递减,猜测是读取传感器B信息的那些延时影响到了计数循环,但是理论上数据流应该是并行的,因此我对这种错误的发生产生了费解。

我想问的问题是:

1、在同一个while循环内,定时循环和平铺式顺序结构是否完全并行运行?

2、有没有方法将读取传感器A和传感器B的定时循环和带有延时的顺序结构分别放到两个同步且并行的循环里,再进行输出?

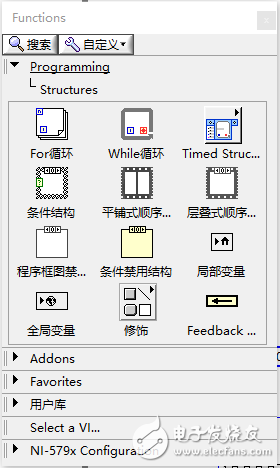

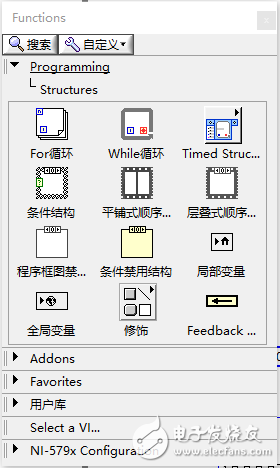

3、我本来想采用事件结构,根据与传感器A信号布尔相交的值的改变进行事件触发,但是FPGA模块中的结构里没有事件结构,采取以下几种结构是否有可能达到我根据一个信号的上升沿同步执行其余操作?

现在我通过设置一个时钟为40MHZ的定时循环读取DIO22 / DIO23 即传感器A的A相和B相信号,通过布尔相交判断其上升沿,每两个上升沿之间进行计数,并在新的上升沿到来时退出该循环。

而读取传感器B的信号是根据时序图配置芯片的引脚电平来实现的,因此添加了平铺式顺序结构,设置了一定的延时留时间给芯片进行配置。

而读取传感器B的信号是根据时序图配置芯片的引脚电平来实现的,因此添加了平铺式顺序结构,设置了一定的延时留时间给芯片进行配置。

上述两个部分均在一个大的while循环中,每执行完一遍以上的程序,就重新开始一次循环。

现在的问题是,当传感器A的信号频率上升到100KHz以上时,计时循环的输出值出现了错误,在同一个周期下计数值呈现规律性递减,猜测是读取传感器B信息的那些延时影响到了计数循环,但是理论上数据流应该是并行的,因此我对这种错误的发生产生了费解。

我想问的问题是:

1、在同一个while循环内,定时循环和平铺式顺序结构是否完全并行运行?

2、有没有方法将读取传感器A和传感器B的定时循环和带有延时的顺序结构分别放到两个同步且并行的循环里,再进行输出?

3、我本来想采用事件结构,根据与传感器A信号布尔相交的值的改变进行事件触发,但是FPGA模块中的结构里没有事件结构,采取以下几种结构是否有可能达到我根据一个信号的上升沿同步执行其余操作?

捞一捞,有没有朋友能提点建议呀?