cRIO使用FIFO情况下的FPGA函数调用

时间:10-02

整理:3721RD

点击:

cRIO采集的模拟量,然后通过FIFO进行传递。在FPGA Target创建DAQ_FPGA.vi,使用FIFO保存采集的模拟量(图2)。运行文件,可以看到数据被采集(只观察了一路信号),程序可以运行(图3)。然后在终端创建DAQ_RT.vi打开FPGA VI引用(图4),但在终端创建的DAQ_RT.vi中调用FPGA失败,但程序没有报错(图5)。因为之前在FPGA没有使用FIFO的情况下,可以被终端的程序成功调用,所以觉得是使用FIFO的方法不对,可能是哪里配置的问题,望大神解惑。

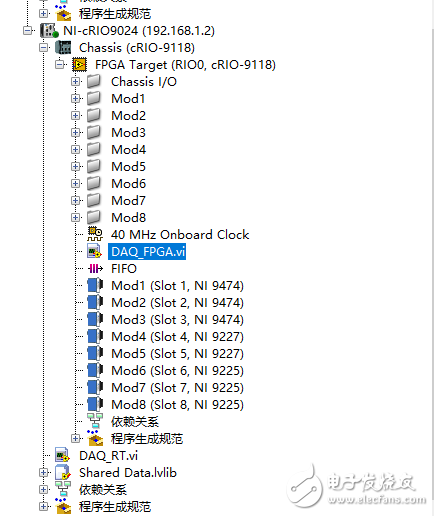

1:项目图

2 FPGA程序图

3 FPGA前面板运行图

4 cRIO程序图

5 cRIO前面板

大家可能都是晚上比较有时间哦 希望小编的问题能够得到解答~

此问答贴被选为2月17日的每日一答贴,活动详情见:http://bbs.elecfans.com/jishu_1111064_1_1.html 希望大家可以踊跃帮助坛友解决问题,谢谢。

多谢管理员,希望大家能不吝赐教

因为接触labview不久,所以问题描述可能不准确。大家有什么看不明白的就直接说吧

在程序结尾增加一个关闭FPGA函数,在FIFO读取的元素数量上设置为非零后解决了问题,大家可以参考一下。

要是连续采集时,RT程序中只要启动一次FPGA程序就可以了,在读取FIFO数据代码处加循环一直采集。