CST 仿真的时域值与屏蔽效能评价

时间:10-02

整理:3721RD

点击:

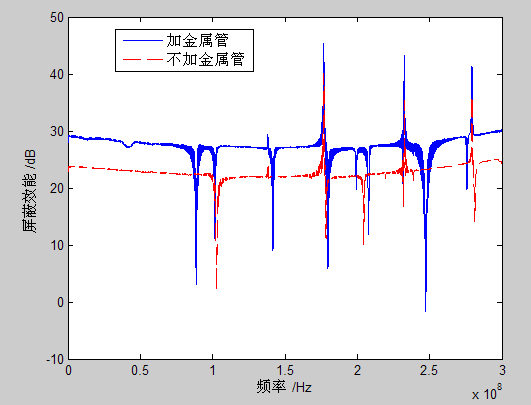

在MS中,仿真带孔腔体,在孔处加孔阵式金属管后可以减少腔体内部的电场值,然后可以计算出加管子与不加管子的电场值和屏蔽效能,仿真加入管后,时域值极大地减小了,证明这个管子具有一定的屏蔽能力,可是当我计算屏蔽效能(频域)时,发现屏蔽效能是有所增加,但也增加了很多的谐振频点,而且谐振频点处的屏蔽效能加入管子后反而降低了,如下图所示,那我该如何评价这个金属管的能力呢?这个管子是有用还是没用呢?

评价一个东西的屏蔽效能是要考虑其屏蔽的频率范围的,

不可能说对全频段进行屏蔽,

但要尽量在较宽的频带内保持较为稳定的屏蔽效能,

即避免谐振点,这就需要进行结构设计了。

对于避免谐振频点有什么好的方法吗?

对于理想结构,可以通过理论来计算谐振点,非理想结构,基本只能通过仿真扫参。

你也可以用等效电路法,但这种方法既不好用,也也不精确。

那有没有具体措施可以消除这个谐振频点?比如按照什么原则改变腔体结果什么的。

可以看看场图在什么地方谐振,然后更改结构,破坏谐振就可以了

你说的场图指的是频域结果图?看频域结果在什么频点处出现波峰,此处即为谐振频点?

就是filed monitor里添加谐振频点的场监视器

只要箱体内设备的工作频率不落在谐振点的附近,确切讲,谐振带宽内,谐振不用可以改变。

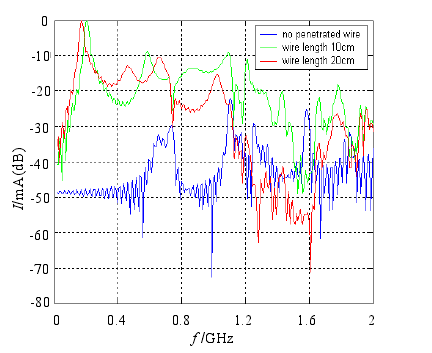

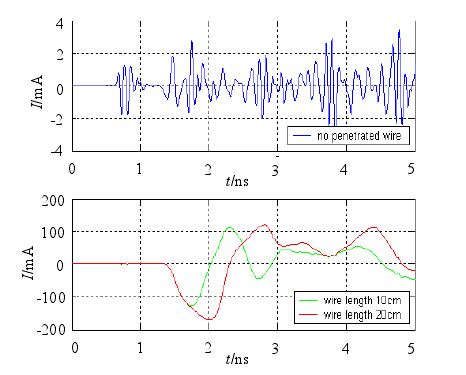

在FDTD中仿真时,在带孔的屏蔽箱体中加上一根贯通导体 发现箱体内电路上的干扰电流大幅度增加。而且随着贯通导体暴露于机箱外部长度增加,干扰电流增强。

这是频域图