CST MWS邊界條件設定對時域訊號的影響

目前是從簡單的例子慢慢學習軟體操作和整體高頻電路的觀念

手邊Run了一個微帶傳輸線

發現邊界條件對於時域訊號影響很巨大

想和大家討論看看

看大家有沒有甚麼想法

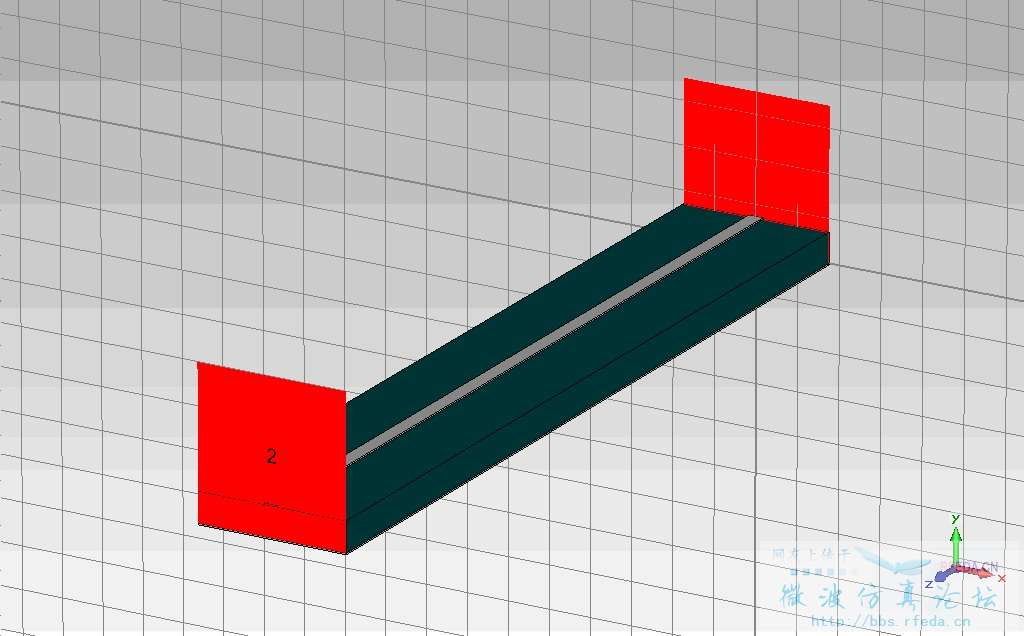

下圖是模型建置

最高求解頻率是 20 Ghz

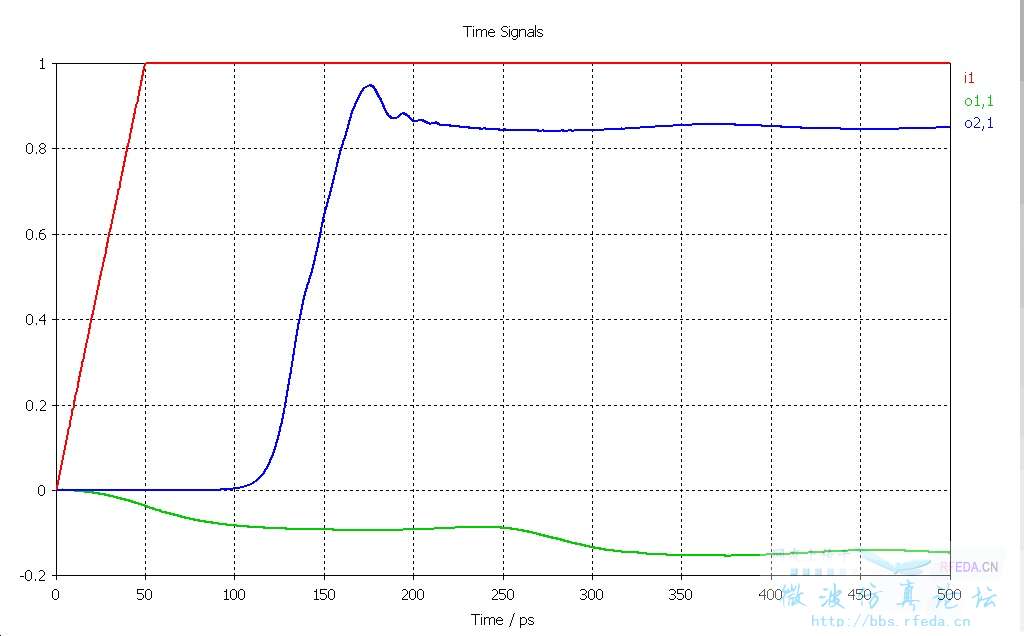

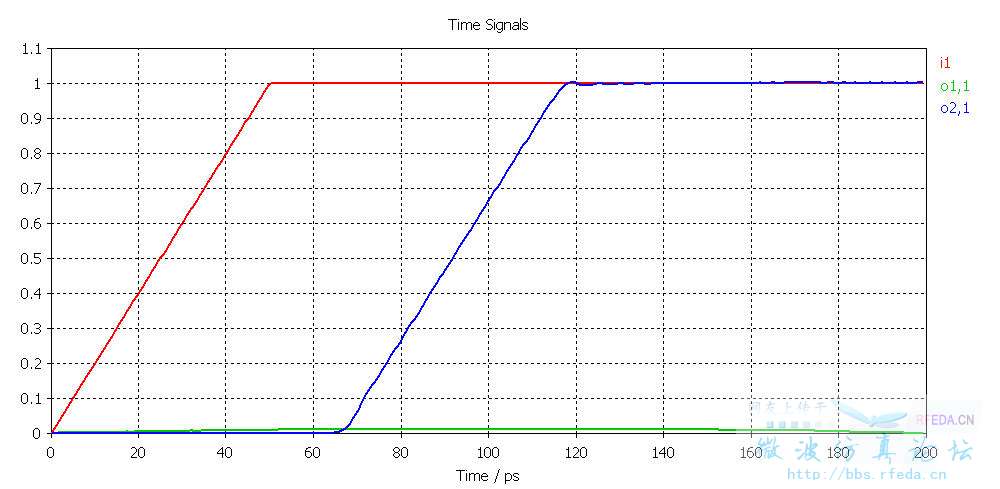

input為rising time 50 ps 的 Step Signal

邊界條件皆設定為Electrical boundary但和模型有一h的間距如下圖

(h為微帶線之高度)

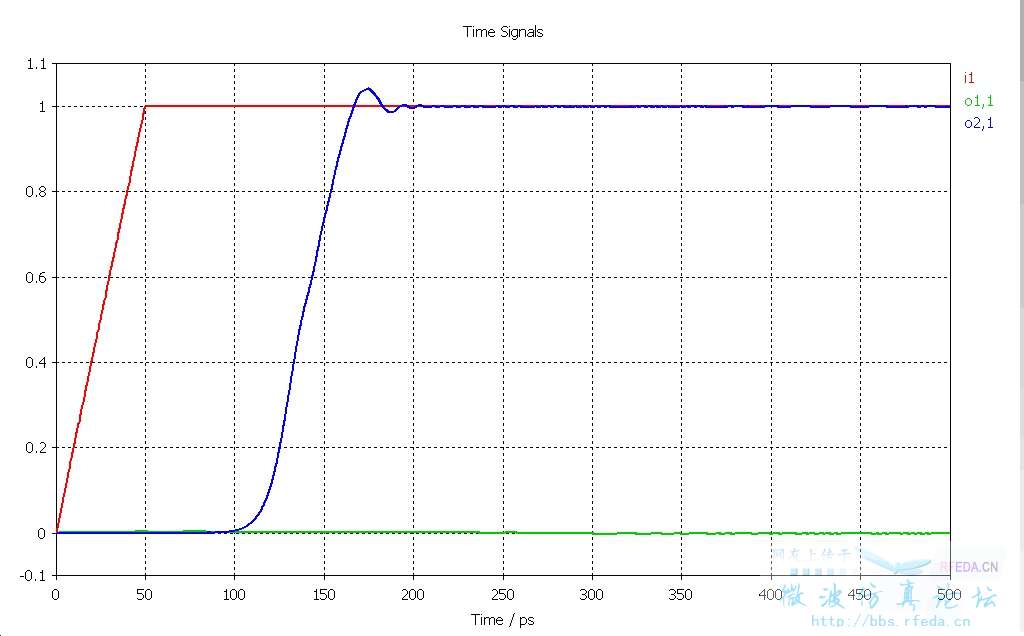

其輸出波型為有反射的訊號如下

理論上因為微帶線結構並無變化

且waveguide port會自動達到阻抗匹配

因此這個結構應該為阻抗匹配且無反射

實驗和理論不符合

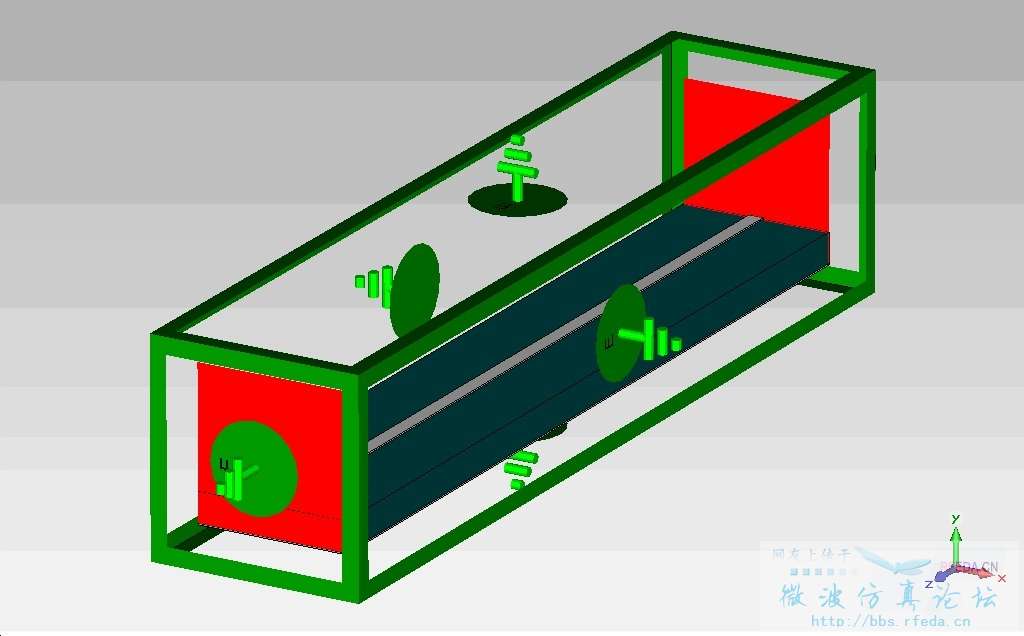

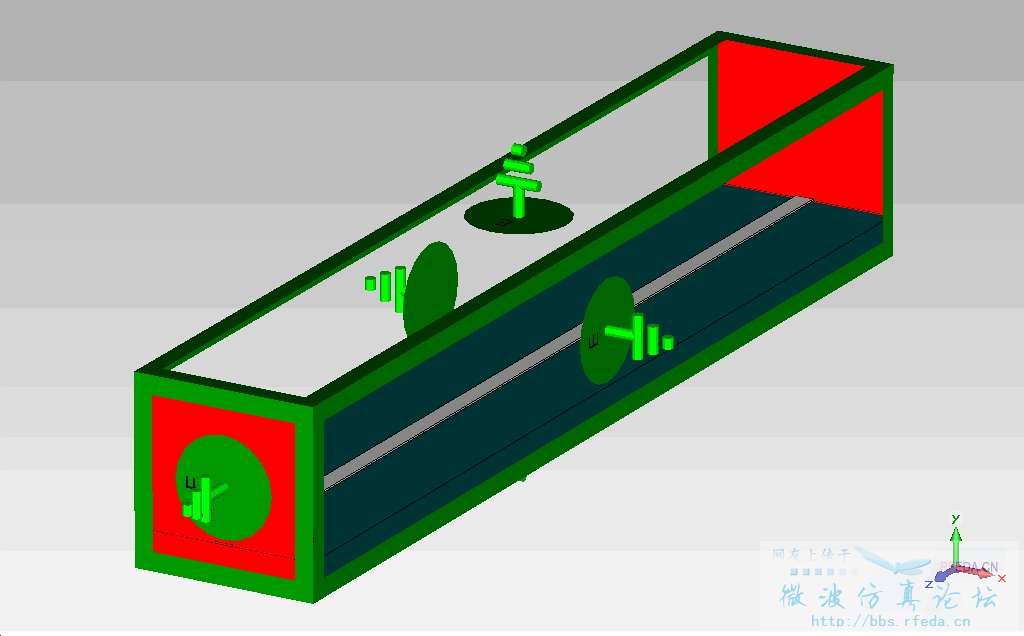

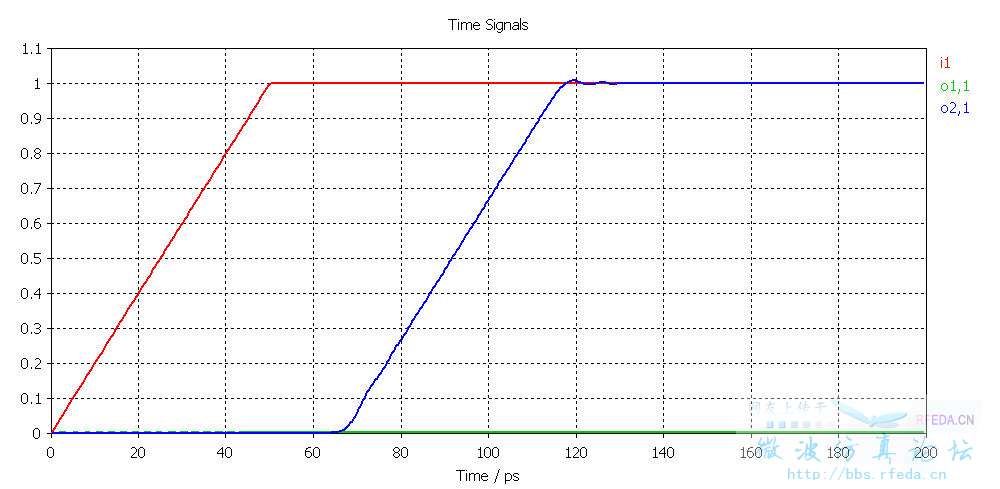

接著將邊界條件設定為和模型緊貼(無間距)如下

邊界條件仍然接為Electrical boundary

其輸出波型為無反射的正常理論波型如下

為什麼會有這樣子的差別小弟想破頭還是無法想通

想和各位討論看看

造成此現象的原因

第一种情况你模拟的相当于是把这个微带线放到一个金属盒子里(盒子比微带线的尺寸大h)的情况,由于PEC边界的反射,会导致传输特新的变化。跟你想模拟的状态是不相符的。

那么第二种情况呢?

我覺得這個問題有可能和CST內數值分析的方法有關

waveguide是一TEM模態的端口,但是microstrip僅能傳遞QTEM

這兩個模態不連續面發生在waveguide port之切面

可能造成求解不準確,或許需要額外設定參數

回到問題本身可能是waveguide port和求解設定沒設定好

而不是與邊界條件有關

但是邊界條件如果緊貼模型會剛好碰到waveguide port的邊界

對於求解可能會有影響,造成剛好求解比較正確

但我目前還未能從仿真驗證我的推論

提供一點想法跟大家一起思考討論

首先推测是这样的,第一种情况下,相当于在波导端口外面加了屏蔽外罩,高次模比较少,第二种情况端口和电壁之间有一段距离,在仿真中有的也要避免这种情况,可能会导致能量发散而不收敛。

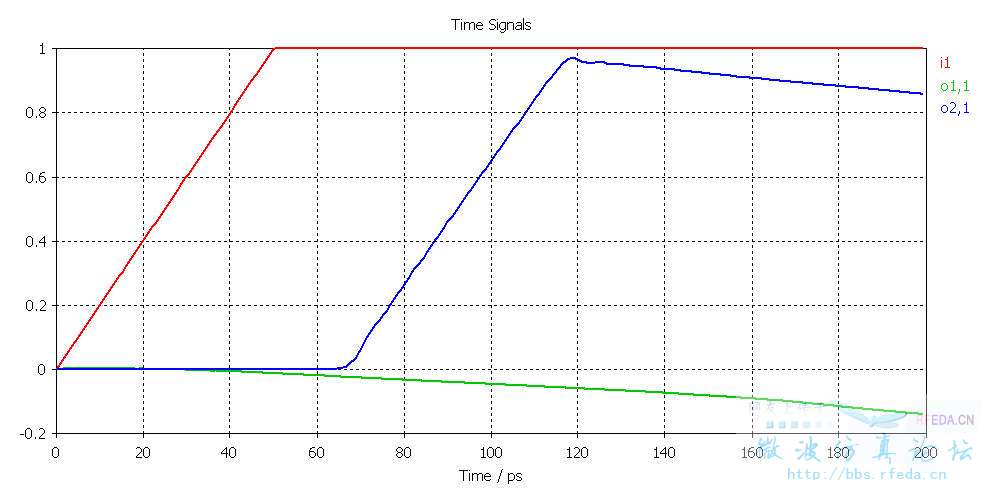

既然是高次模的影响,对这种设想进行验证,过程如下:

从上面可以看出来,就是高次模引起的,给端口加了屏蔽之后和边界紧贴结构的结果是一样的

這個論壇真的是臥虎藏龍

Hawk好猛一下就解出來了

另外想問一下

甚麼時候會需要增加Electric shielding

有沒有甚麼經驗法則判斷

畢竟如果模型較為複雜我並無法判斷甚麼是正確的仿真結果

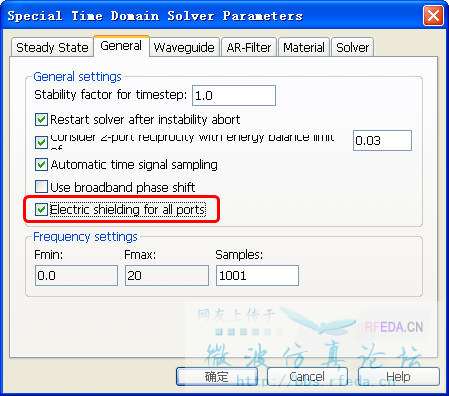

此外我翻了一下幫助文件

Electric shielding for all ports:

A perfectly shielding (PEC) frame surrounding each waveguide port region will be added.

This option causes higher reflections at ports.

Therefore, it should only be used if a calculation has become unstable.

裡面提到應該要當計算不穩定時才需要設定這個選項

但我的仿真解果似乎計算是穩定的?

依照幫助文件似乎不該加這個條件?

還希望神人幫忙解答一下

感謝萬分

1波端口与电边界之间的那一段距离在没有shielding的情况下,cst是如何处理的?当作真空还是电边界?

2你的上图很好的证明了紧贴跟shielding的效果是一样的,而shielding是说波段口被pec包围,也就是把我1中所说的空间看作pec了,这时候没有反射(可以认为匹配了)。这个可以用cst验证把1中所述空间堵上pec,而波段口不加shielding来验证。

因而,上图并不能说明不加shielding的情况下产生了高次模,而反射是由高次模引起。

如果用open,或者添加了surrounding的electric,那么waveguide port就变成了internal waveguide port。这个时候添加shielding才能看到区别。

1的話如果沒有增加shielding,則waveguide port是以magnetic作計算

這個在waveguide port overview的幫助文件裡面有提到

1.我看一了遍waveguide port overview,恕我愚钝,没找到你所说的“waveguide port是以magnetic作計算”

2.我不知道你是否看明白我的问题,我不是问waveguide port是以什么做计算的(waveguide port其实是一个无限长的波导,如果覆盖整个横截面的话,相当于一个匹配负载),而是问waveguide port与上下边界之间的空间是如何处理的。

没太看明白,您老这最后一句话是想表达什么意思啊?是说这两种情况下都应该添加shielding吗?

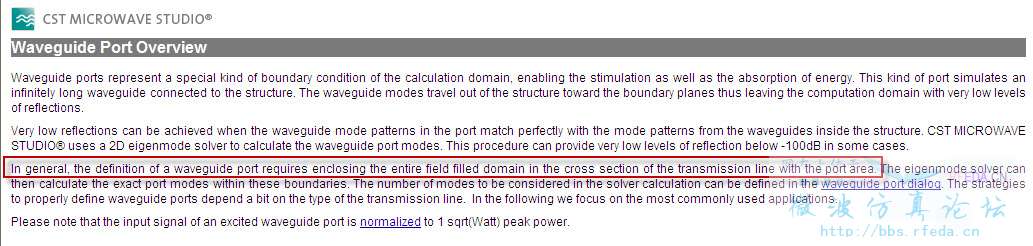

又仔细看了一遍《Waveguide Port Overview》,里面有这么一句话“In general, the definition of a waveguide port requires enclosing the entirefield filled domain in the cross section of the transmission line with the portarea. ” 也就是说设置的波端口应该覆盖传输线横截面上的所有场填充区域。

在小编的第一个例子中,Waveguide Port与电边界区域之间区域也应该有场分布,而其设置Waveguide Port并没有满足上述要求。故第一个例子应该属于对Waveguide Port的错误使用,得到的结果不符合理论也就没什么奇怪了。

就是说,对于设置在close boundary处的waveguide port,已经有所谓的"shielding"了。只有在open或者close boundary但设置了surrounding space,那么设置在计算区域之内的internal waveguide port要添加shielding,否则有可能会造成unstable。

ytfbuaa大人,您英明神武

是小的愚鈍才來跟大家請教

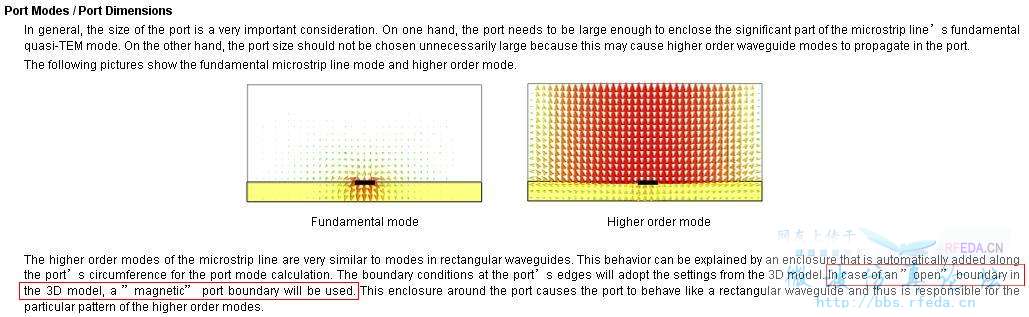

上面有提到如果3d模型是"Open",則"magnectic"邊界就會被採用

不過不知道我這樣斷章取義有沒有誤解

從port mode看起來場分布在靠近waveguide port的邊界附近就變得很小且很稀疏

(以最大的scale去看,並取log)

因此覺得外圍場分布應該更少

不過後來加大waveguide port邊界似乎反射量有變少

但是會出現higher mode的warning

目前仍然在克服不過先來回報XD

小弟的目標是希望邊界條件對於模型的影響能夠越小越好

畢竟實際上並不會有電邊界在我DUT的旁邊

因此如果+shielding可能會讓仿真失真

這樣就失去使用仿真軟體的意義了