12.5G锁相环设计调试的心路历程

时间:10-02

整理:3721RD

点击:

亲爱的网友们,终于,我回来了。带着满身疲倦又面带微笑的回来了。这次我要跟大家分享一下我最近3个月断断续续设计加调试的12.5G锁相环的心路历程。经过3个月挣扎,有了不错的成果,也想发文记录下过程。既当是一种总结,也是一种交流分享。锁相环(PLL),这个东西本来课程就没怎么学过,对其中的原理不是非常懂,然后就半学半设计的做了。选用的芯片是Hittite的HMC807,12.4-13.4G的集成VCO的PLL芯片。因为老师规定外壳是5cmx4cm,而这款芯片需要5V,3V,以及最高15V的VCO驱动电压。因为FR4的板基已经不能承受那么高频率,所以采用罗杰斯(ROGERS)板材。但是,这种板子做四层太贵,只能两层,而且,要放在盒子里,反面不能放元件。当时就跟老师说了这个我也没信心做出来会好,只有试试。第一版光布局就用了很长时间,因为有几个规定必须保证:退偶电容必须离电源脚越近越好;模拟电源与数字电源必须用磁珠隔离,15V电源通过DC-DC升压,而众所周知,开关电源噪声很容易毁了整块射频板的性能。结果做下来相噪只有40dbc。果断不能用啊~最后,两层板的方案告吹,四层板就用FR4,衰落大的话输出线就离射频口近点嘛,秉着这种想法,就进行了四层板的设计。四层板的性能明显比两层板好多了嘛,1M地方相噪117dbc,芯片手册是132,已经可以接受了,毕竟我的PCB水平也只是自己积累的,并没有高手系统的带我过,所以我还是很满意的(希望高人可以帮我指点指点)。但板子好了之后,调试就成大问题了。理论缺乏啊!先上图:

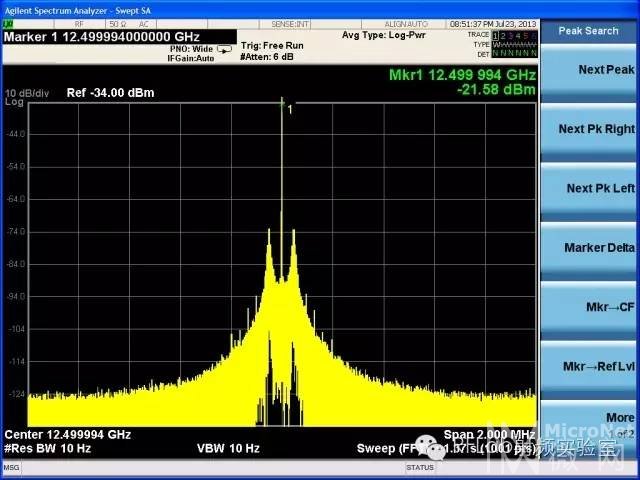

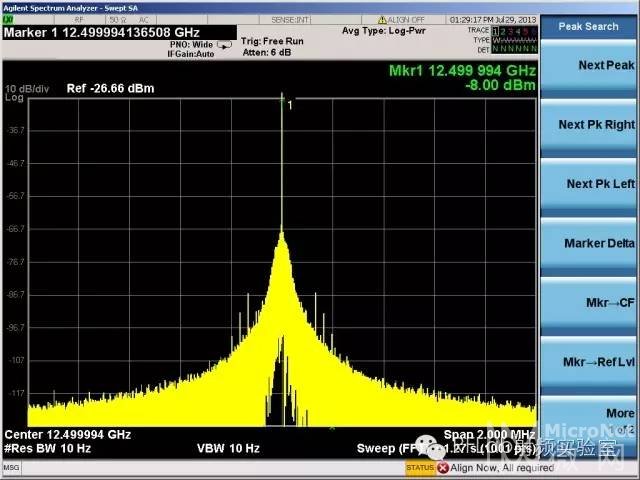

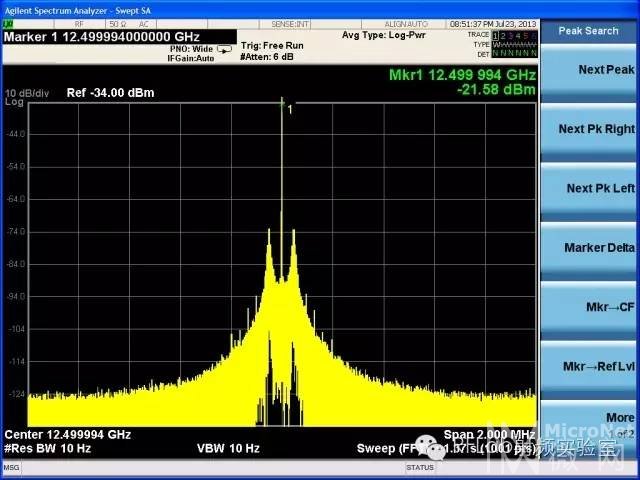

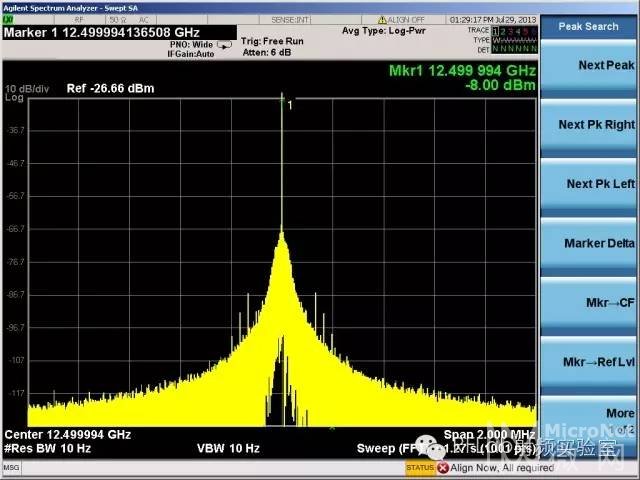

上图中可以看出12.45G边上有两个肩膀看,拉开就是下边显示的那样。真搞不懂是什么东西造成这样的杂散信号。我用的reference是25M的。而且这样的波形我在网上都没查到,网上说的参考杂散,小数分频杂散都不是长这个样子的。这叫我一个纠结啊!起初我怀疑是不是电源不够干净导致的电源杂散。然后我把所有模拟电源部分多添了几种小电容,而且割掉板子,加了磁珠,但是信号根本不怎么变(可能变了吧,反正我是么看出来)。怎么办,纠结啊,自己不懂啊。然后我就怀疑是环路滤波器设计问题。但是,是环路滤波器的什么问题呢?天无绝人之路,碰到个大神,他看了这个波形后说是环路滤波器相位裕度不够造成的。要在50-60之间最好。之前真没关心过这个概念。我记忆当中只有放大器要相位裕度防止自激。但是hittite没有专门的环路滤波器设计软件。没办法,就用ADI的ADISIMPLL凑合凑合。环路滤波器初始带宽应为鉴相频率的1/10,如果能成功锁住可以继续减小环路带宽。这个经验公式也是我这次做项目才知道的(之前真是菜啊)。然后,我鉴相频率为25MHz,最后调整带宽到190KHz,相位裕度55°,效果如图:

上图中可以看出12.45G边上有两个肩膀看,拉开就是下边显示的那样。真搞不懂是什么东西造成这样的杂散信号。我用的reference是25M的。而且这样的波形我在网上都没查到,网上说的参考杂散,小数分频杂散都不是长这个样子的。这叫我一个纠结啊!起初我怀疑是不是电源不够干净导致的电源杂散。然后我把所有模拟电源部分多添了几种小电容,而且割掉板子,加了磁珠,但是信号根本不怎么变(可能变了吧,反正我是么看出来)。怎么办,纠结啊,自己不懂啊。然后我就怀疑是环路滤波器设计问题。但是,是环路滤波器的什么问题呢?天无绝人之路,碰到个大神,他看了这个波形后说是环路滤波器相位裕度不够造成的。要在50-60之间最好。之前真没关心过这个概念。我记忆当中只有放大器要相位裕度防止自激。但是hittite没有专门的环路滤波器设计软件。没办法,就用ADI的ADISIMPLL凑合凑合。环路滤波器初始带宽应为鉴相频率的1/10,如果能成功锁住可以继续减小环路带宽。这个经验公式也是我这次做项目才知道的(之前真是菜啊)。然后,我鉴相频率为25MHz,最后调整带宽到190KHz,相位裕度55°,效果如图:

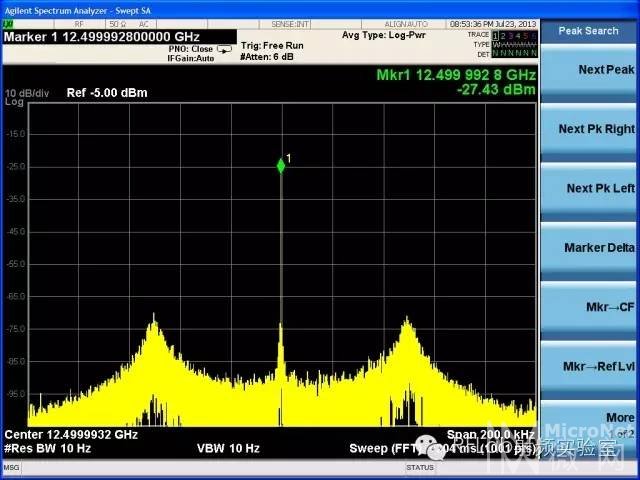

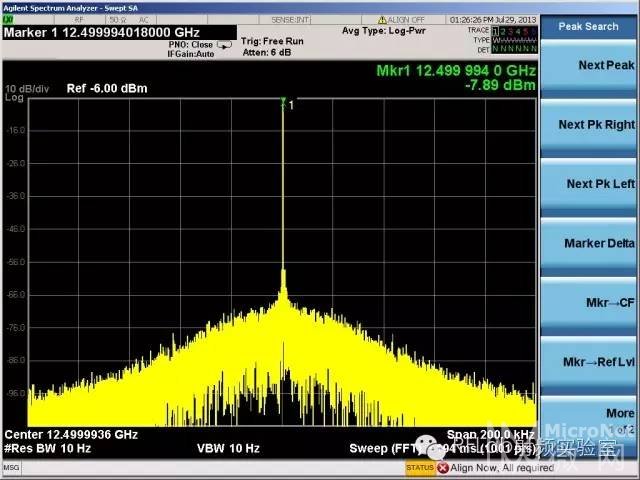

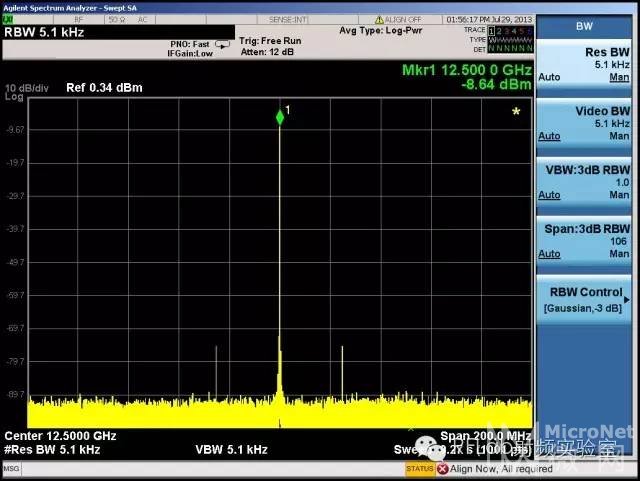

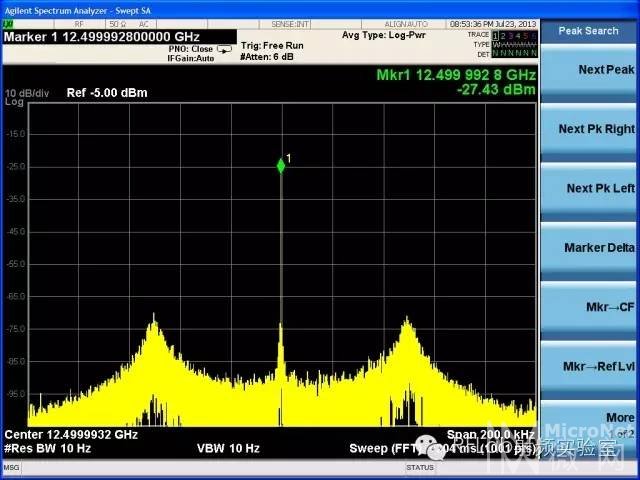

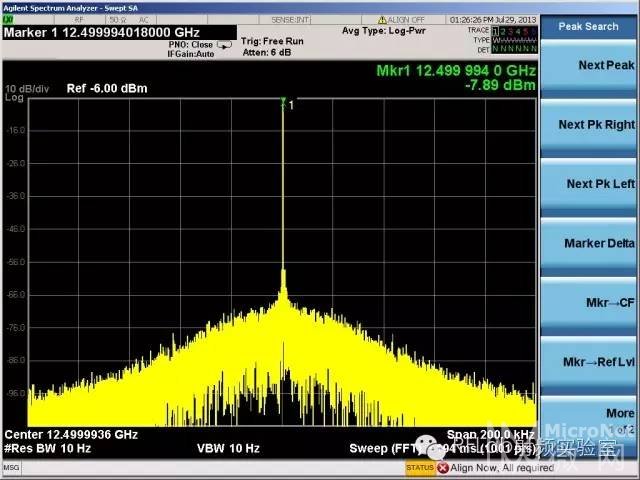

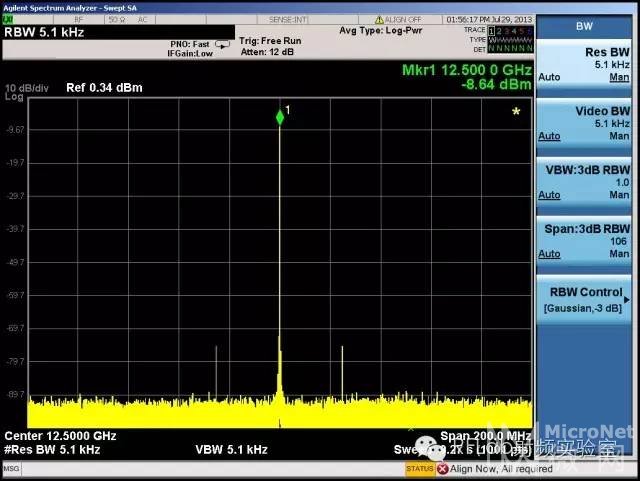

拉大之后发现肩膀明显改善,但还是有~,天秤座的我要求能再好一点,最好一点肩膀都没有。然后又用ADI的软件设计了几种参数,始终去不掉。ADI的软件里自然没有hittite芯片的模型,所以仿真的毕竟不能当饭吃。最后,我投靠了强大的ADS。AGILENT的荣誉产品。里面的PLL的DESIGNGUIDE很好的解决了问题。所有仿真参数打进去,出来的滤波器参数非常精准。直接看图说话:

拉大之后发现肩膀明显改善,但还是有~,天秤座的我要求能再好一点,最好一点肩膀都没有。然后又用ADI的软件设计了几种参数,始终去不掉。ADI的软件里自然没有hittite芯片的模型,所以仿真的毕竟不能当饭吃。最后,我投靠了强大的ADS。AGILENT的荣誉产品。里面的PLL的DESIGNGUIDE很好的解决了问题。所有仿真参数打进去,出来的滤波器参数非常精准。直接看图说话:

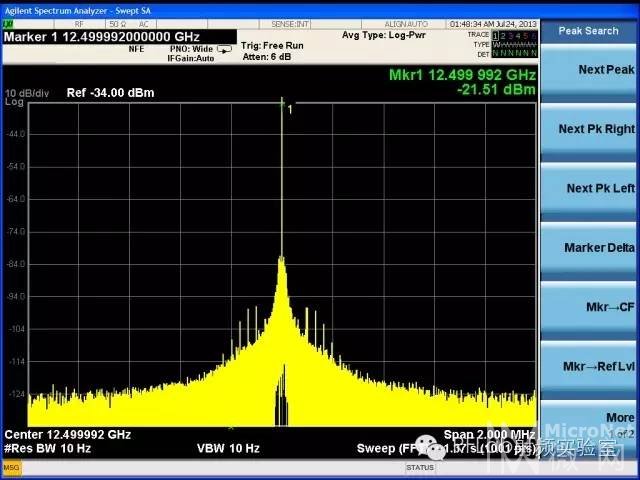

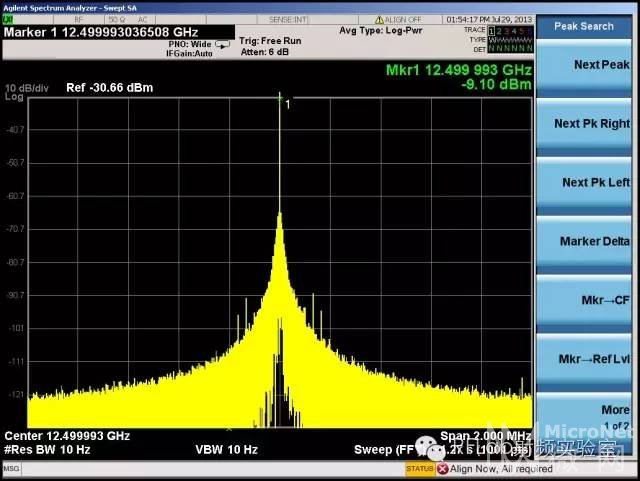

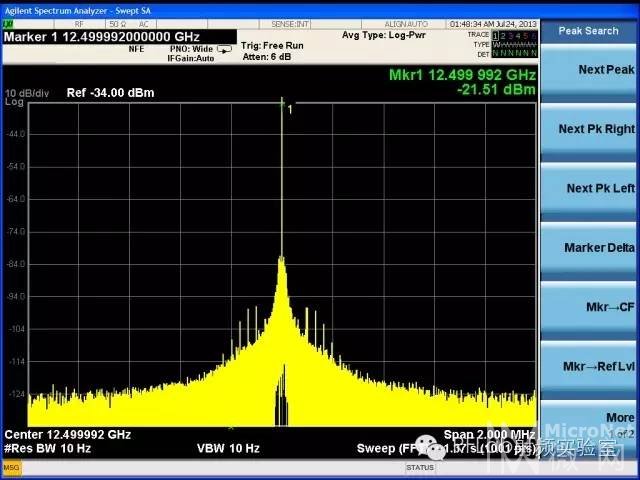

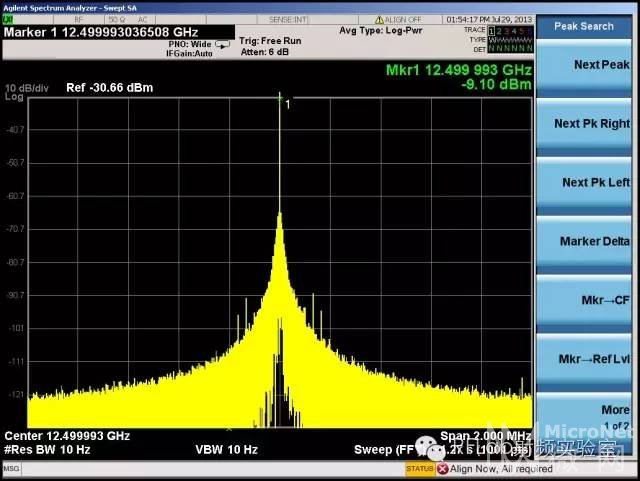

上图中完全看不出肩膀,拉开看。这也太难看了吧,这么胖,怎么办,为什么这么胖我到现在也还没搞清楚。望高人指点一二。我想到的唯一办法就是减小环路带宽看看会不会好。我也知道环路带宽太小会造成同步带过小,容易失锁,锁定时间也大大加长。但菜鸟的我没有办法了。就这么招了,我继续减小环路带宽。最后到了10kHz的50°相位裕度,已经是鉴相频率25MHz的1/2500了~,继续上图:

上图中完全看不出肩膀,拉开看。这也太难看了吧,这么胖,怎么办,为什么这么胖我到现在也还没搞清楚。望高人指点一二。我想到的唯一办法就是减小环路带宽看看会不会好。我也知道环路带宽太小会造成同步带过小,容易失锁,锁定时间也大大加长。但菜鸟的我没有办法了。就这么招了,我继续减小环路带宽。最后到了10kHz的50°相位裕度,已经是鉴相频率25MHz的1/2500了~,继续上图:

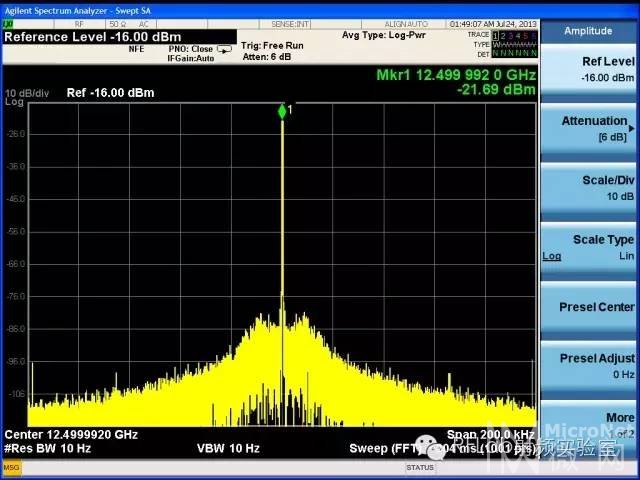

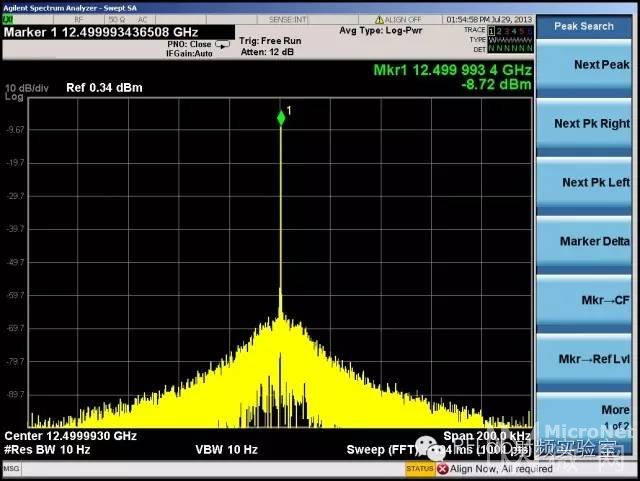

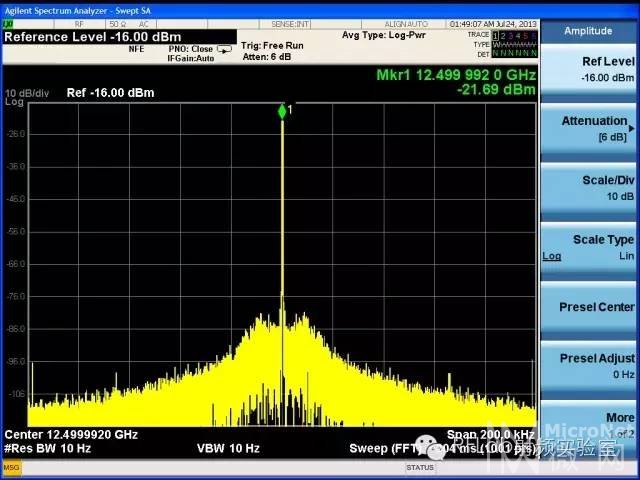

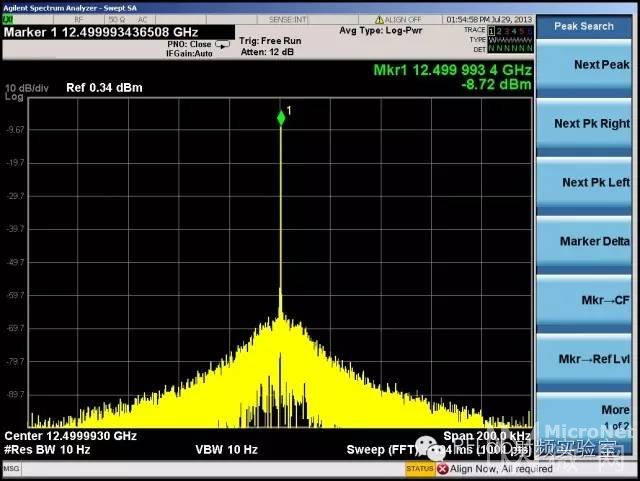

现在看上去舒服多了,但我觉得还是有点胖,但我已经不敢再减小了,我总觉得应该有其他办法让他变瘦。而且,图中边上的小毛刺从一开始的图中就有,这个真心也不知道怎么来的,我配置PLL的单片机在配置完成后连晶振都让他停掉了,所以不可能是单片机造成,而且这一版中去掉了开关电源,板子上全部是LDO,接入的电源也是线性恒流源。相当高级的那种。所以就真心不知道了。 减小环路带宽有点好处,就是参考杂散得到很好的抑制。但因为我的鉴相频率太低,只有25M,所以,不能完全滤除。上大图:

现在看上去舒服多了,但我觉得还是有点胖,但我已经不敢再减小了,我总觉得应该有其他办法让他变瘦。而且,图中边上的小毛刺从一开始的图中就有,这个真心也不知道怎么来的,我配置PLL的单片机在配置完成后连晶振都让他停掉了,所以不可能是单片机造成,而且这一版中去掉了开关电源,板子上全部是LDO,接入的电源也是线性恒流源。相当高级的那种。所以就真心不知道了。 减小环路带宽有点好处,就是参考杂散得到很好的抑制。但因为我的鉴相频率太低,只有25M,所以,不能完全滤除。上大图:

边上两根小的间隔为25MHz,这个就是参考杂散。不断的减小环路带宽这个的衰减程度肉眼看得很明显。这样已经差不多了,算出具成效,装进盒子里可以使用了。虽然如此,但是我总觉得有点遗憾,有很多问题我还是没有搞懂。虽然已经懂了不少。把历程写下来,各位看官如果懂的话请不吝指教,我真心想学点东西。但又不想看锁相技术的书,都是公式看不进,也不实用,跟波形对不起来。所以,如果哪位知道这个肩膀叫什么专业名字,跟什么有关,怎么去除,对于现在这个还是有点胖的波形如何进一步“减肥”,有见解的,希望多多留言哈。我一来想精益求精,二来想来讨教点东西,三是记录点滴,日后自己看起来也当个调试记录吧。

边上两根小的间隔为25MHz,这个就是参考杂散。不断的减小环路带宽这个的衰减程度肉眼看得很明显。这样已经差不多了,算出具成效,装进盒子里可以使用了。虽然如此,但是我总觉得有点遗憾,有很多问题我还是没有搞懂。虽然已经懂了不少。把历程写下来,各位看官如果懂的话请不吝指教,我真心想学点东西。但又不想看锁相技术的书,都是公式看不进,也不实用,跟波形对不起来。所以,如果哪位知道这个肩膀叫什么专业名字,跟什么有关,怎么去除,对于现在这个还是有点胖的波形如何进一步“减肥”,有见解的,希望多多留言哈。我一来想精益求精,二来想来讨教点东西,三是记录点滴,日后自己看起来也当个调试记录吧。

本文来源:oceancjc的博客

本文来源:oceancjc的博客

公众号RFLab射频实验室

公众号RFLab射频实验室

上图中可以看出12.45G边上有两个肩膀看,拉开就是下边显示的那样。真搞不懂是什么东西造成这样的杂散信号。我用的reference是25M的。而且这样的波形我在网上都没查到,网上说的参考杂散,小数分频杂散都不是长这个样子的。这叫我一个纠结啊!起初我怀疑是不是电源不够干净导致的电源杂散。然后我把所有模拟电源部分多添了几种小电容,而且割掉板子,加了磁珠,但是信号根本不怎么变(可能变了吧,反正我是么看出来)。怎么办,纠结啊,自己不懂啊。然后我就怀疑是环路滤波器设计问题。但是,是环路滤波器的什么问题呢?天无绝人之路,碰到个大神,他看了这个波形后说是环路滤波器相位裕度不够造成的。要在50-60之间最好。之前真没关心过这个概念。我记忆当中只有放大器要相位裕度防止自激。但是hittite没有专门的环路滤波器设计软件。没办法,就用ADI的ADISIMPLL凑合凑合。环路滤波器初始带宽应为鉴相频率的1/10,如果能成功锁住可以继续减小环路带宽。这个经验公式也是我这次做项目才知道的(之前真是菜啊)。然后,我鉴相频率为25MHz,最后调整带宽到190KHz,相位裕度55°,效果如图:

上图中可以看出12.45G边上有两个肩膀看,拉开就是下边显示的那样。真搞不懂是什么东西造成这样的杂散信号。我用的reference是25M的。而且这样的波形我在网上都没查到,网上说的参考杂散,小数分频杂散都不是长这个样子的。这叫我一个纠结啊!起初我怀疑是不是电源不够干净导致的电源杂散。然后我把所有模拟电源部分多添了几种小电容,而且割掉板子,加了磁珠,但是信号根本不怎么变(可能变了吧,反正我是么看出来)。怎么办,纠结啊,自己不懂啊。然后我就怀疑是环路滤波器设计问题。但是,是环路滤波器的什么问题呢?天无绝人之路,碰到个大神,他看了这个波形后说是环路滤波器相位裕度不够造成的。要在50-60之间最好。之前真没关心过这个概念。我记忆当中只有放大器要相位裕度防止自激。但是hittite没有专门的环路滤波器设计软件。没办法,就用ADI的ADISIMPLL凑合凑合。环路滤波器初始带宽应为鉴相频率的1/10,如果能成功锁住可以继续减小环路带宽。这个经验公式也是我这次做项目才知道的(之前真是菜啊)。然后,我鉴相频率为25MHz,最后调整带宽到190KHz,相位裕度55°,效果如图:

拉大之后发现肩膀明显改善,但还是有~,天秤座的我要求能再好一点,最好一点肩膀都没有。然后又用ADI的软件设计了几种参数,始终去不掉。ADI的软件里自然没有hittite芯片的模型,所以仿真的毕竟不能当饭吃。最后,我投靠了强大的ADS。AGILENT的荣誉产品。里面的PLL的DESIGNGUIDE很好的解决了问题。所有仿真参数打进去,出来的滤波器参数非常精准。直接看图说话:

拉大之后发现肩膀明显改善,但还是有~,天秤座的我要求能再好一点,最好一点肩膀都没有。然后又用ADI的软件设计了几种参数,始终去不掉。ADI的软件里自然没有hittite芯片的模型,所以仿真的毕竟不能当饭吃。最后,我投靠了强大的ADS。AGILENT的荣誉产品。里面的PLL的DESIGNGUIDE很好的解决了问题。所有仿真参数打进去,出来的滤波器参数非常精准。直接看图说话:

上图中完全看不出肩膀,拉开看。这也太难看了吧,这么胖,怎么办,为什么这么胖我到现在也还没搞清楚。望高人指点一二。我想到的唯一办法就是减小环路带宽看看会不会好。我也知道环路带宽太小会造成同步带过小,容易失锁,锁定时间也大大加长。但菜鸟的我没有办法了。就这么招了,我继续减小环路带宽。最后到了10kHz的50°相位裕度,已经是鉴相频率25MHz的1/2500了~,继续上图:

上图中完全看不出肩膀,拉开看。这也太难看了吧,这么胖,怎么办,为什么这么胖我到现在也还没搞清楚。望高人指点一二。我想到的唯一办法就是减小环路带宽看看会不会好。我也知道环路带宽太小会造成同步带过小,容易失锁,锁定时间也大大加长。但菜鸟的我没有办法了。就这么招了,我继续减小环路带宽。最后到了10kHz的50°相位裕度,已经是鉴相频率25MHz的1/2500了~,继续上图:

现在看上去舒服多了,但我觉得还是有点胖,但我已经不敢再减小了,我总觉得应该有其他办法让他变瘦。而且,图中边上的小毛刺从一开始的图中就有,这个真心也不知道怎么来的,我配置PLL的单片机在配置完成后连晶振都让他停掉了,所以不可能是单片机造成,而且这一版中去掉了开关电源,板子上全部是LDO,接入的电源也是线性恒流源。相当高级的那种。所以就真心不知道了。 减小环路带宽有点好处,就是参考杂散得到很好的抑制。但因为我的鉴相频率太低,只有25M,所以,不能完全滤除。上大图:

现在看上去舒服多了,但我觉得还是有点胖,但我已经不敢再减小了,我总觉得应该有其他办法让他变瘦。而且,图中边上的小毛刺从一开始的图中就有,这个真心也不知道怎么来的,我配置PLL的单片机在配置完成后连晶振都让他停掉了,所以不可能是单片机造成,而且这一版中去掉了开关电源,板子上全部是LDO,接入的电源也是线性恒流源。相当高级的那种。所以就真心不知道了。 减小环路带宽有点好处,就是参考杂散得到很好的抑制。但因为我的鉴相频率太低,只有25M,所以,不能完全滤除。上大图: 边上两根小的间隔为25MHz,这个就是参考杂散。不断的减小环路带宽这个的衰减程度肉眼看得很明显。这样已经差不多了,算出具成效,装进盒子里可以使用了。虽然如此,但是我总觉得有点遗憾,有很多问题我还是没有搞懂。虽然已经懂了不少。把历程写下来,各位看官如果懂的话请不吝指教,我真心想学点东西。但又不想看锁相技术的书,都是公式看不进,也不实用,跟波形对不起来。所以,如果哪位知道这个肩膀叫什么专业名字,跟什么有关,怎么去除,对于现在这个还是有点胖的波形如何进一步“减肥”,有见解的,希望多多留言哈。我一来想精益求精,二来想来讨教点东西,三是记录点滴,日后自己看起来也当个调试记录吧。

边上两根小的间隔为25MHz,这个就是参考杂散。不断的减小环路带宽这个的衰减程度肉眼看得很明显。这样已经差不多了,算出具成效,装进盒子里可以使用了。虽然如此,但是我总觉得有点遗憾,有很多问题我还是没有搞懂。虽然已经懂了不少。把历程写下来,各位看官如果懂的话请不吝指教,我真心想学点东西。但又不想看锁相技术的书,都是公式看不进,也不实用,跟波形对不起来。所以,如果哪位知道这个肩膀叫什么专业名字,跟什么有关,怎么去除,对于现在这个还是有点胖的波形如何进一步“减肥”,有见解的,希望多多留言哈。我一来想精益求精,二来想来讨教点东西,三是记录点滴,日后自己看起来也当个调试记录吧。 本文来源:oceancjc的博客

本文来源:oceancjc的博客

公众号RFLab射频实验室

公众号RFLab射频实验室

牛