7nm功耗问题及解决方案,设计成功源于能够实现精确预测,稳健可靠的RTL到GDS方法

时间:10-02

整理:3721RD

点击:

戳上面的蓝字关注我们哦!

7nm工艺不仅能将速度提升35%,功耗锐减65%,而且还能实现3.3倍的更高密度,这些优势似乎使其顺理成章地成为新一代片上系统(SoC)设计的不二之选。但是将一块中端7nm SoC芯片投入量产估计需要约2.71亿美元的总体设计成本和500人年的工作量,企业需要仔细权衡在这一先进技术节点上开展设计的成本和产出。为赢得利润,设计团队需要管理成本和资源,确保让芯片一次性成功。这些考量因素需要设计方法将重心向早期分析转移,从而形成更明智的下游决策并及时发现设计问题。对于更小节点上的设计而言,功耗和电源噪声管理仍然是一个重大问题,而且它们也是减少设计失效的关键要求。7nm finFET节点上的更大器件电容、互连电阻和电流密度愈发凸显出动态功耗和热管理的重要性。通过采用可预测并且十分可靠的RTL方法,您能够在这个流程中尽早发现和纠正潜在的功耗问题,制定更出色的设计决策。尽早做出设计决策 RTL功耗分析通过提供更加直观的环境,方便用户发现、调试和修改潜在的功耗问题,从而在设计流中尽早实现具有重要影响的功耗相关决策。与通过综合和计算门级功耗流程所需的数小时相比,RTL功耗分析可在短短几分钟内完成。此外,在RTL上仿真更高覆盖率的设计翻转也容易得多。所有这些优势让您能够探索多种架构,在各种工作模式下做出最优设计决策。AMD在近期的《ANSYS Advantage》文章中介绍到,通过在各种不同带宽情境中严格地跟踪RTL功耗,他们成功地在高性能计算设计应用中将功耗锐降70%。

7nm工艺不仅能将速度提升35%,功耗锐减65%,而且还能实现3.3倍的更高密度,这些优势似乎使其顺理成章地成为新一代片上系统(SoC)设计的不二之选。但是将一块中端7nm SoC芯片投入量产估计需要约2.71亿美元的总体设计成本和500人年的工作量,企业需要仔细权衡在这一先进技术节点上开展设计的成本和产出。为赢得利润,设计团队需要管理成本和资源,确保让芯片一次性成功。这些考量因素需要设计方法将重心向早期分析转移,从而形成更明智的下游决策并及时发现设计问题。对于更小节点上的设计而言,功耗和电源噪声管理仍然是一个重大问题,而且它们也是减少设计失效的关键要求。7nm finFET节点上的更大器件电容、互连电阻和电流密度愈发凸显出动态功耗和热管理的重要性。通过采用可预测并且十分可靠的RTL方法,您能够在这个流程中尽早发现和纠正潜在的功耗问题,制定更出色的设计决策。尽早做出设计决策 RTL功耗分析通过提供更加直观的环境,方便用户发现、调试和修改潜在的功耗问题,从而在设计流中尽早实现具有重要影响的功耗相关决策。与通过综合和计算门级功耗流程所需的数小时相比,RTL功耗分析可在短短几分钟内完成。此外,在RTL上仿真更高覆盖率的设计翻转也容易得多。所有这些优势让您能够探索多种架构,在各种工作模式下做出最优设计决策。AMD在近期的《ANSYS Advantage》文章中介绍到,通过在各种不同带宽情境中严格地跟踪RTL功耗,他们成功地在高性能计算设计应用中将功耗锐降70%。

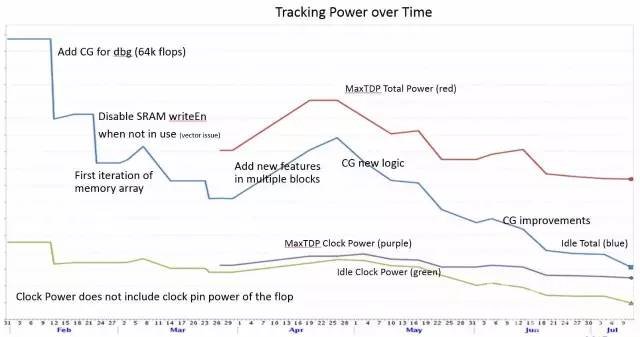

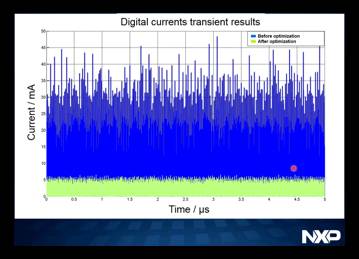

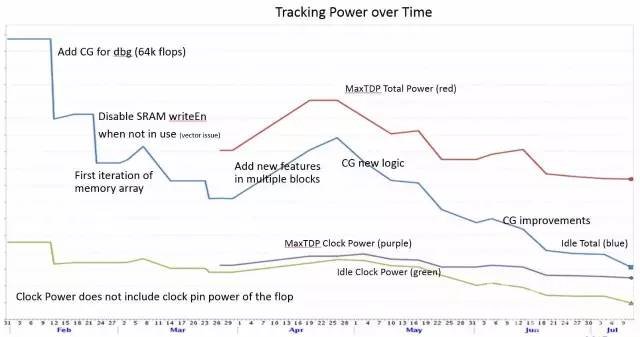

图1:为大幅度降低功耗,在多种不同带宽情境下开展RTL功耗研究(来源:ANSYS Advantage)精确预测功耗 为尽早制定设计决策,RTL结果应可靠地预测已实现设计的最终功耗。这要求在RTL和物理设计间建立紧密链接,在RTL级工作阶段为例如时钟分配网络、连线电容、缓冲器和毛刺等实际的物理设计细节建立模型。对于时钟网络而言,RTL功耗的可预测性和准确性至关重要。先进节点要求RTL时钟功耗建模考虑时钟网络的物理结构、时序和功耗约束以及时钟线的互连电容。此外,毛刺功耗也对预测功耗的准确性有显著影响,因此需要对毛刺生成逻辑路径的传播过程进行RTL建模和分析。通过以物理方式开展时序感知时钟树综合(CTS)、毛刺功耗建模与仿真、连线电容和其他物理效应的建模,您能够预测它们对总功耗的影响,并胸有成竹地尽早做出设计决策。消除冗余翻转 消除冗余翻转是管理动态功耗的关键一环。时钟线具有最大驱动负载的高翻转连线,并控制着大部分的总功耗。毛刺功耗可占到总逻辑功耗的20%到30%,特别是在高计算强度的设计中尤为如此。RTL功耗效率指标是一种非常有效的方法,便于您了解这些浪费功耗的区域。在RTL上工作能在每个周期了解时钟、控制和数据信号间的翻转关联性,而这种关联性对于准确的存储器和时钟门控效率分析非常有用。此外,基于RTL的功耗仿真还能进行复杂的分析,自动找出针对时钟、时序逻辑和存在毛刺倾向的数据路径逻辑的RTL改动,以解决多余的翻转问题,从而为下游工具提供有效补充。RTL在更高的设计抽象级工作,能够分析非常大型的设计,因此也能分析出由于模块之间相互作用而浪费的功耗。而这一点是使用其他实现工具无法企及的。实际上,NXP在ANSYS网络研讨会中曾提到他们如何利用RTL功耗分析和降耗功能来调试和解决数字逻辑的噪声干扰问题。这些干扰曾给他们的汽车信息娱乐应用的模拟组件造成不利影响。

图1:为大幅度降低功耗,在多种不同带宽情境下开展RTL功耗研究(来源:ANSYS Advantage)精确预测功耗 为尽早制定设计决策,RTL结果应可靠地预测已实现设计的最终功耗。这要求在RTL和物理设计间建立紧密链接,在RTL级工作阶段为例如时钟分配网络、连线电容、缓冲器和毛刺等实际的物理设计细节建立模型。对于时钟网络而言,RTL功耗的可预测性和准确性至关重要。先进节点要求RTL时钟功耗建模考虑时钟网络的物理结构、时序和功耗约束以及时钟线的互连电容。此外,毛刺功耗也对预测功耗的准确性有显著影响,因此需要对毛刺生成逻辑路径的传播过程进行RTL建模和分析。通过以物理方式开展时序感知时钟树综合(CTS)、毛刺功耗建模与仿真、连线电容和其他物理效应的建模,您能够预测它们对总功耗的影响,并胸有成竹地尽早做出设计决策。消除冗余翻转 消除冗余翻转是管理动态功耗的关键一环。时钟线具有最大驱动负载的高翻转连线,并控制着大部分的总功耗。毛刺功耗可占到总逻辑功耗的20%到30%,特别是在高计算强度的设计中尤为如此。RTL功耗效率指标是一种非常有效的方法,便于您了解这些浪费功耗的区域。在RTL上工作能在每个周期了解时钟、控制和数据信号间的翻转关联性,而这种关联性对于准确的存储器和时钟门控效率分析非常有用。此外,基于RTL的功耗仿真还能进行复杂的分析,自动找出针对时钟、时序逻辑和存在毛刺倾向的数据路径逻辑的RTL改动,以解决多余的翻转问题,从而为下游工具提供有效补充。RTL在更高的设计抽象级工作,能够分析非常大型的设计,因此也能分析出由于模块之间相互作用而浪费的功耗。而这一点是使用其他实现工具无法企及的。实际上,NXP在ANSYS网络研讨会中曾提到他们如何利用RTL功耗分析和降耗功能来调试和解决数字逻辑的噪声干扰问题。这些干扰曾给他们的汽车信息娱乐应用的模拟组件造成不利影响。

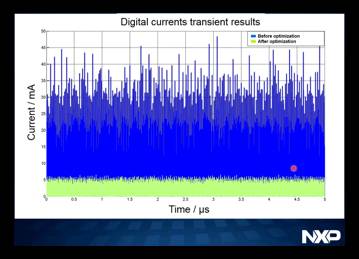

图2:NXP利用RTL功耗方法减少数字噪声干扰(来源:ANSYS)实际应用的翻转分析 功耗行为与芯片翻转高度相关。传统用于识别适当翻转模式的方法重点关注功耗分析的短期时间窗口,这样可能会漏掉芯片在实际翻转下可能发生的功耗关键型事件,因此存在一些弊端。例如在操作系统(OS)启动或高分辨率视频帧应用场景,尽早掌握实际应用的功耗和热特性,,可帮助您有效避免在设计流程后期出现成本高昂的功耗相关问题。硬件加速仿真器等专业硬件能够以更高的速度仿真,让基于实际应用的分析得以实现。但是针对这种实际应用翻转逐周期地开展功耗分析需要高强度的计算,并花费数天乃至数周的时间。利用高性能RTL仿真引擎,您能够为非常长的波形在每个周期生成精确的功耗特性分析,并且速度比传统方法要快几个数量级。这样就能在几小时内完成包含数十毫秒翻转的高清视频帧的功耗计算工作,以及在一天内完成包含数百毫秒数据的操作系统启动的功耗特性分析。将波形翻转数据从仿真器直接传输到RTL引擎中,还能将运行时间加快5倍到10倍。推动早期电源噪声和热分析 快速运行数百万个周期的数千个RTL波形,能够提供众多关键信息。它能发现重要活动,例如导致大电源噪声和热点的峰值开关功率(di/dt)。通过重点关注功率关键型翻转事件,您能够提升瞬态供电网络分析的覆盖范围和效率,并降低设计失效风险。此外,基于实际应用的RTL芯片电流特性分析还能尽早实现芯片、封装和电路板的准确协同设计。在系统级,功耗对于热性能具有直接影响。了解整个实际仿真过程中的功率特性有助于您确定和解决消耗最大功率、进而造成热问题的设计区域。通过回归分析跟踪功耗 在整个设计过程中监测功耗数据,可确保下游设计变更不会给其功耗性能造成不利影响。功率回归分析能提供关于各种降耗措施的有效性的反馈,并跟踪多种工作模式下的功率效率。查询数据库并且跨多种设计版本比较结果的功能,可让您避免后续设计变更造成的意外问题。管理大型设计 由于芯片大小及其功能继续以指数速率增长,仔细分析多种工作情境时有效管理计算的能力将成为重要的成功标准。将弹性计算和大数据分析等新兴技术应用到RTL功耗分析能够有助于管理这种复杂性。总而言之,功耗仍旧是7nm工艺上的主要设计难点。为了成功地在这个先进节点上交付设计,您需要采取早期分析来实现以下目标: 考量物理设计因素准确地预测功耗 发现具有较大影响的降耗机会并消除浪费的翻转 通过分析实际应用中的功耗特性,提高电源噪声和热分析的覆盖范围 监测设计变更后和各种工作模式下的功耗效率 充分发挥弹性计算和大数据分析的功能和性能部署可预测和可靠的RTL功耗方法能帮助您实现更快的设计收敛。

图2:NXP利用RTL功耗方法减少数字噪声干扰(来源:ANSYS)实际应用的翻转分析 功耗行为与芯片翻转高度相关。传统用于识别适当翻转模式的方法重点关注功耗分析的短期时间窗口,这样可能会漏掉芯片在实际翻转下可能发生的功耗关键型事件,因此存在一些弊端。例如在操作系统(OS)启动或高分辨率视频帧应用场景,尽早掌握实际应用的功耗和热特性,,可帮助您有效避免在设计流程后期出现成本高昂的功耗相关问题。硬件加速仿真器等专业硬件能够以更高的速度仿真,让基于实际应用的分析得以实现。但是针对这种实际应用翻转逐周期地开展功耗分析需要高强度的计算,并花费数天乃至数周的时间。利用高性能RTL仿真引擎,您能够为非常长的波形在每个周期生成精确的功耗特性分析,并且速度比传统方法要快几个数量级。这样就能在几小时内完成包含数十毫秒翻转的高清视频帧的功耗计算工作,以及在一天内完成包含数百毫秒数据的操作系统启动的功耗特性分析。将波形翻转数据从仿真器直接传输到RTL引擎中,还能将运行时间加快5倍到10倍。推动早期电源噪声和热分析 快速运行数百万个周期的数千个RTL波形,能够提供众多关键信息。它能发现重要活动,例如导致大电源噪声和热点的峰值开关功率(di/dt)。通过重点关注功率关键型翻转事件,您能够提升瞬态供电网络分析的覆盖范围和效率,并降低设计失效风险。此外,基于实际应用的RTL芯片电流特性分析还能尽早实现芯片、封装和电路板的准确协同设计。在系统级,功耗对于热性能具有直接影响。了解整个实际仿真过程中的功率特性有助于您确定和解决消耗最大功率、进而造成热问题的设计区域。通过回归分析跟踪功耗 在整个设计过程中监测功耗数据,可确保下游设计变更不会给其功耗性能造成不利影响。功率回归分析能提供关于各种降耗措施的有效性的反馈,并跟踪多种工作模式下的功率效率。查询数据库并且跨多种设计版本比较结果的功能,可让您避免后续设计变更造成的意外问题。管理大型设计 由于芯片大小及其功能继续以指数速率增长,仔细分析多种工作情境时有效管理计算的能力将成为重要的成功标准。将弹性计算和大数据分析等新兴技术应用到RTL功耗分析能够有助于管理这种复杂性。总而言之,功耗仍旧是7nm工艺上的主要设计难点。为了成功地在这个先进节点上交付设计,您需要采取早期分析来实现以下目标: 考量物理设计因素准确地预测功耗 发现具有较大影响的降耗机会并消除浪费的翻转 通过分析实际应用中的功耗特性,提高电源噪声和热分析的覆盖范围 监测设计变更后和各种工作模式下的功耗效率 充分发挥弹性计算和大数据分析的功能和性能部署可预测和可靠的RTL功耗方法能帮助您实现更快的设计收敛。

欢迎关注《计算机辅助工程》微信平台——公众微信号:CAEChina,您也可以直接扫描或者常按如下二维码关注本平台。

欢迎关注《计算机辅助工程》微信平台——公众微信号:CAEChina,您也可以直接扫描或者常按如下二维码关注本平台。

本平台的命令如下:1、回复"ZXZX"查询最新资讯:回复"GWZX"过往资讯2、回复"ML"查当期目录3、回复"WZ"查期刊网址4、回复"JJ"查期刊简介5、回复"LXFX"查编辑部联系方式6、回复“ZZCX”查询自主创新CAE相关资讯7、回复"ANSYS"查询ANSYS公司资讯8、回复"Midas"查询迈达斯公司资讯9、回复"SIPESC"查询大连集创信息技术有限公司资讯10、回复“SIEMENS"或者"LMS"查询西门子公司资讯11、回复“MSC”查询MSC公司咨询12、回复"XBK”查询CAE软件操作小百科13、回复"HP"查询相关命令

本平台的命令如下:1、回复"ZXZX"查询最新资讯:回复"GWZX"过往资讯2、回复"ML"查当期目录3、回复"WZ"查期刊网址4、回复"JJ"查期刊简介5、回复"LXFX"查编辑部联系方式6、回复“ZZCX”查询自主创新CAE相关资讯7、回复"ANSYS"查询ANSYS公司资讯8、回复"Midas"查询迈达斯公司资讯9、回复"SIPESC"查询大连集创信息技术有限公司资讯10、回复“SIEMENS"或者"LMS"查询西门子公司资讯11、回复“MSC”查询MSC公司咨询12、回复"XBK”查询CAE软件操作小百科13、回复"HP"查询相关命令

7nm工艺不仅能将速度提升35%,功耗锐减65%,而且还能实现3.3倍的更高密度,这些优势似乎使其顺理成章地成为新一代片上系统(SoC)设计的不二之选。但是将一块中端7nm SoC芯片投入量产估计需要约2.71亿美元的总体设计成本和500人年的工作量,企业需要仔细权衡在这一先进技术节点上开展设计的成本和产出。为赢得利润,设计团队需要管理成本和资源,确保让芯片一次性成功。这些考量因素需要设计方法将重心向早期分析转移,从而形成更明智的下游决策并及时发现设计问题。对于更小节点上的设计而言,功耗和电源噪声管理仍然是一个重大问题,而且它们也是减少设计失效的关键要求。7nm finFET节点上的更大器件电容、互连电阻和电流密度愈发凸显出动态功耗和热管理的重要性。通过采用可预测并且十分可靠的RTL方法,您能够在这个流程中尽早发现和纠正潜在的功耗问题,制定更出色的设计决策。尽早做出设计决策 RTL功耗分析通过提供更加直观的环境,方便用户发现、调试和修改潜在的功耗问题,从而在设计流中尽早实现具有重要影响的功耗相关决策。与通过综合和计算门级功耗流程所需的数小时相比,RTL功耗分析可在短短几分钟内完成。此外,在RTL上仿真更高覆盖率的设计翻转也容易得多。所有这些优势让您能够探索多种架构,在各种工作模式下做出最优设计决策。AMD在近期的《ANSYS Advantage》文章中介绍到,通过在各种不同带宽情境中严格地跟踪RTL功耗,他们成功地在高性能计算设计应用中将功耗锐降70%。

7nm工艺不仅能将速度提升35%,功耗锐减65%,而且还能实现3.3倍的更高密度,这些优势似乎使其顺理成章地成为新一代片上系统(SoC)设计的不二之选。但是将一块中端7nm SoC芯片投入量产估计需要约2.71亿美元的总体设计成本和500人年的工作量,企业需要仔细权衡在这一先进技术节点上开展设计的成本和产出。为赢得利润,设计团队需要管理成本和资源,确保让芯片一次性成功。这些考量因素需要设计方法将重心向早期分析转移,从而形成更明智的下游决策并及时发现设计问题。对于更小节点上的设计而言,功耗和电源噪声管理仍然是一个重大问题,而且它们也是减少设计失效的关键要求。7nm finFET节点上的更大器件电容、互连电阻和电流密度愈发凸显出动态功耗和热管理的重要性。通过采用可预测并且十分可靠的RTL方法,您能够在这个流程中尽早发现和纠正潜在的功耗问题,制定更出色的设计决策。尽早做出设计决策 RTL功耗分析通过提供更加直观的环境,方便用户发现、调试和修改潜在的功耗问题,从而在设计流中尽早实现具有重要影响的功耗相关决策。与通过综合和计算门级功耗流程所需的数小时相比,RTL功耗分析可在短短几分钟内完成。此外,在RTL上仿真更高覆盖率的设计翻转也容易得多。所有这些优势让您能够探索多种架构,在各种工作模式下做出最优设计决策。AMD在近期的《ANSYS Advantage》文章中介绍到,通过在各种不同带宽情境中严格地跟踪RTL功耗,他们成功地在高性能计算设计应用中将功耗锐降70%。 图1:为大幅度降低功耗,在多种不同带宽情境下开展RTL功耗研究(来源:ANSYS Advantage)精确预测功耗 为尽早制定设计决策,RTL结果应可靠地预测已实现设计的最终功耗。这要求在RTL和物理设计间建立紧密链接,在RTL级工作阶段为例如时钟分配网络、连线电容、缓冲器和毛刺等实际的物理设计细节建立模型。对于时钟网络而言,RTL功耗的可预测性和准确性至关重要。先进节点要求RTL时钟功耗建模考虑时钟网络的物理结构、时序和功耗约束以及时钟线的互连电容。此外,毛刺功耗也对预测功耗的准确性有显著影响,因此需要对毛刺生成逻辑路径的传播过程进行RTL建模和分析。通过以物理方式开展时序感知时钟树综合(CTS)、毛刺功耗建模与仿真、连线电容和其他物理效应的建模,您能够预测它们对总功耗的影响,并胸有成竹地尽早做出设计决策。消除冗余翻转 消除冗余翻转是管理动态功耗的关键一环。时钟线具有最大驱动负载的高翻转连线,并控制着大部分的总功耗。毛刺功耗可占到总逻辑功耗的20%到30%,特别是在高计算强度的设计中尤为如此。RTL功耗效率指标是一种非常有效的方法,便于您了解这些浪费功耗的区域。在RTL上工作能在每个周期了解时钟、控制和数据信号间的翻转关联性,而这种关联性对于准确的存储器和时钟门控效率分析非常有用。此外,基于RTL的功耗仿真还能进行复杂的分析,自动找出针对时钟、时序逻辑和存在毛刺倾向的数据路径逻辑的RTL改动,以解决多余的翻转问题,从而为下游工具提供有效补充。RTL在更高的设计抽象级工作,能够分析非常大型的设计,因此也能分析出由于模块之间相互作用而浪费的功耗。而这一点是使用其他实现工具无法企及的。实际上,NXP在ANSYS网络研讨会中曾提到他们如何利用RTL功耗分析和降耗功能来调试和解决数字逻辑的噪声干扰问题。这些干扰曾给他们的汽车信息娱乐应用的模拟组件造成不利影响。

图1:为大幅度降低功耗,在多种不同带宽情境下开展RTL功耗研究(来源:ANSYS Advantage)精确预测功耗 为尽早制定设计决策,RTL结果应可靠地预测已实现设计的最终功耗。这要求在RTL和物理设计间建立紧密链接,在RTL级工作阶段为例如时钟分配网络、连线电容、缓冲器和毛刺等实际的物理设计细节建立模型。对于时钟网络而言,RTL功耗的可预测性和准确性至关重要。先进节点要求RTL时钟功耗建模考虑时钟网络的物理结构、时序和功耗约束以及时钟线的互连电容。此外,毛刺功耗也对预测功耗的准确性有显著影响,因此需要对毛刺生成逻辑路径的传播过程进行RTL建模和分析。通过以物理方式开展时序感知时钟树综合(CTS)、毛刺功耗建模与仿真、连线电容和其他物理效应的建模,您能够预测它们对总功耗的影响,并胸有成竹地尽早做出设计决策。消除冗余翻转 消除冗余翻转是管理动态功耗的关键一环。时钟线具有最大驱动负载的高翻转连线,并控制着大部分的总功耗。毛刺功耗可占到总逻辑功耗的20%到30%,特别是在高计算强度的设计中尤为如此。RTL功耗效率指标是一种非常有效的方法,便于您了解这些浪费功耗的区域。在RTL上工作能在每个周期了解时钟、控制和数据信号间的翻转关联性,而这种关联性对于准确的存储器和时钟门控效率分析非常有用。此外,基于RTL的功耗仿真还能进行复杂的分析,自动找出针对时钟、时序逻辑和存在毛刺倾向的数据路径逻辑的RTL改动,以解决多余的翻转问题,从而为下游工具提供有效补充。RTL在更高的设计抽象级工作,能够分析非常大型的设计,因此也能分析出由于模块之间相互作用而浪费的功耗。而这一点是使用其他实现工具无法企及的。实际上,NXP在ANSYS网络研讨会中曾提到他们如何利用RTL功耗分析和降耗功能来调试和解决数字逻辑的噪声干扰问题。这些干扰曾给他们的汽车信息娱乐应用的模拟组件造成不利影响。 图2:NXP利用RTL功耗方法减少数字噪声干扰(来源:ANSYS)实际应用的翻转分析 功耗行为与芯片翻转高度相关。传统用于识别适当翻转模式的方法重点关注功耗分析的短期时间窗口,这样可能会漏掉芯片在实际翻转下可能发生的功耗关键型事件,因此存在一些弊端。例如在操作系统(OS)启动或高分辨率视频帧应用场景,尽早掌握实际应用的功耗和热特性,,可帮助您有效避免在设计流程后期出现成本高昂的功耗相关问题。硬件加速仿真器等专业硬件能够以更高的速度仿真,让基于实际应用的分析得以实现。但是针对这种实际应用翻转逐周期地开展功耗分析需要高强度的计算,并花费数天乃至数周的时间。利用高性能RTL仿真引擎,您能够为非常长的波形在每个周期生成精确的功耗特性分析,并且速度比传统方法要快几个数量级。这样就能在几小时内完成包含数十毫秒翻转的高清视频帧的功耗计算工作,以及在一天内完成包含数百毫秒数据的操作系统启动的功耗特性分析。将波形翻转数据从仿真器直接传输到RTL引擎中,还能将运行时间加快5倍到10倍。推动早期电源噪声和热分析 快速运行数百万个周期的数千个RTL波形,能够提供众多关键信息。它能发现重要活动,例如导致大电源噪声和热点的峰值开关功率(di/dt)。通过重点关注功率关键型翻转事件,您能够提升瞬态供电网络分析的覆盖范围和效率,并降低设计失效风险。此外,基于实际应用的RTL芯片电流特性分析还能尽早实现芯片、封装和电路板的准确协同设计。在系统级,功耗对于热性能具有直接影响。了解整个实际仿真过程中的功率特性有助于您确定和解决消耗最大功率、进而造成热问题的设计区域。通过回归分析跟踪功耗 在整个设计过程中监测功耗数据,可确保下游设计变更不会给其功耗性能造成不利影响。功率回归分析能提供关于各种降耗措施的有效性的反馈,并跟踪多种工作模式下的功率效率。查询数据库并且跨多种设计版本比较结果的功能,可让您避免后续设计变更造成的意外问题。管理大型设计 由于芯片大小及其功能继续以指数速率增长,仔细分析多种工作情境时有效管理计算的能力将成为重要的成功标准。将弹性计算和大数据分析等新兴技术应用到RTL功耗分析能够有助于管理这种复杂性。总而言之,功耗仍旧是7nm工艺上的主要设计难点。为了成功地在这个先进节点上交付设计,您需要采取早期分析来实现以下目标: 考量物理设计因素准确地预测功耗 发现具有较大影响的降耗机会并消除浪费的翻转 通过分析实际应用中的功耗特性,提高电源噪声和热分析的覆盖范围 监测设计变更后和各种工作模式下的功耗效率 充分发挥弹性计算和大数据分析的功能和性能部署可预测和可靠的RTL功耗方法能帮助您实现更快的设计收敛。

图2:NXP利用RTL功耗方法减少数字噪声干扰(来源:ANSYS)实际应用的翻转分析 功耗行为与芯片翻转高度相关。传统用于识别适当翻转模式的方法重点关注功耗分析的短期时间窗口,这样可能会漏掉芯片在实际翻转下可能发生的功耗关键型事件,因此存在一些弊端。例如在操作系统(OS)启动或高分辨率视频帧应用场景,尽早掌握实际应用的功耗和热特性,,可帮助您有效避免在设计流程后期出现成本高昂的功耗相关问题。硬件加速仿真器等专业硬件能够以更高的速度仿真,让基于实际应用的分析得以实现。但是针对这种实际应用翻转逐周期地开展功耗分析需要高强度的计算,并花费数天乃至数周的时间。利用高性能RTL仿真引擎,您能够为非常长的波形在每个周期生成精确的功耗特性分析,并且速度比传统方法要快几个数量级。这样就能在几小时内完成包含数十毫秒翻转的高清视频帧的功耗计算工作,以及在一天内完成包含数百毫秒数据的操作系统启动的功耗特性分析。将波形翻转数据从仿真器直接传输到RTL引擎中,还能将运行时间加快5倍到10倍。推动早期电源噪声和热分析 快速运行数百万个周期的数千个RTL波形,能够提供众多关键信息。它能发现重要活动,例如导致大电源噪声和热点的峰值开关功率(di/dt)。通过重点关注功率关键型翻转事件,您能够提升瞬态供电网络分析的覆盖范围和效率,并降低设计失效风险。此外,基于实际应用的RTL芯片电流特性分析还能尽早实现芯片、封装和电路板的准确协同设计。在系统级,功耗对于热性能具有直接影响。了解整个实际仿真过程中的功率特性有助于您确定和解决消耗最大功率、进而造成热问题的设计区域。通过回归分析跟踪功耗 在整个设计过程中监测功耗数据,可确保下游设计变更不会给其功耗性能造成不利影响。功率回归分析能提供关于各种降耗措施的有效性的反馈,并跟踪多种工作模式下的功率效率。查询数据库并且跨多种设计版本比较结果的功能,可让您避免后续设计变更造成的意外问题。管理大型设计 由于芯片大小及其功能继续以指数速率增长,仔细分析多种工作情境时有效管理计算的能力将成为重要的成功标准。将弹性计算和大数据分析等新兴技术应用到RTL功耗分析能够有助于管理这种复杂性。总而言之,功耗仍旧是7nm工艺上的主要设计难点。为了成功地在这个先进节点上交付设计,您需要采取早期分析来实现以下目标: 考量物理设计因素准确地预测功耗 发现具有较大影响的降耗机会并消除浪费的翻转 通过分析实际应用中的功耗特性,提高电源噪声和热分析的覆盖范围 监测设计变更后和各种工作模式下的功耗效率 充分发挥弹性计算和大数据分析的功能和性能部署可预测和可靠的RTL功耗方法能帮助您实现更快的设计收敛。  欢迎关注《计算机辅助工程》微信平台——公众微信号:CAEChina,您也可以直接扫描或者常按如下二维码关注本平台。

欢迎关注《计算机辅助工程》微信平台——公众微信号:CAEChina,您也可以直接扫描或者常按如下二维码关注本平台。 本平台的命令如下:1、回复"ZXZX"查询最新资讯:回复"GWZX"过往资讯2、回复"ML"查当期目录3、回复"WZ"查期刊网址4、回复"JJ"查期刊简介5、回复"LXFX"查编辑部联系方式6、回复“ZZCX”查询自主创新CAE相关资讯7、回复"ANSYS"查询ANSYS公司资讯8、回复"Midas"查询迈达斯公司资讯9、回复"SIPESC"查询大连集创信息技术有限公司资讯10、回复“SIEMENS"或者"LMS"查询西门子公司资讯11、回复“MSC”查询MSC公司咨询12、回复"XBK”查询CAE软件操作小百科13、回复"HP"查询相关命令

本平台的命令如下:1、回复"ZXZX"查询最新资讯:回复"GWZX"过往资讯2、回复"ML"查当期目录3、回复"WZ"查期刊网址4、回复"JJ"查期刊简介5、回复"LXFX"查编辑部联系方式6、回复“ZZCX”查询自主创新CAE相关资讯7、回复"ANSYS"查询ANSYS公司资讯8、回复"Midas"查询迈达斯公司资讯9、回复"SIPESC"查询大连集创信息技术有限公司资讯10、回复“SIEMENS"或者"LMS"查询西门子公司资讯11、回复“MSC”查询MSC公司咨询12、回复"XBK”查询CAE软件操作小百科13、回复"HP"查询相关命令