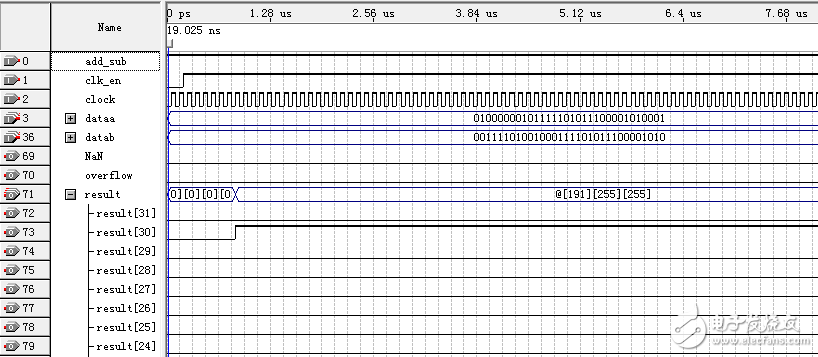

Quartus II 中的宏功能模块altfp_add_sub的仿真测试结果不正确

时间:10-02

整理:3721RD

点击:

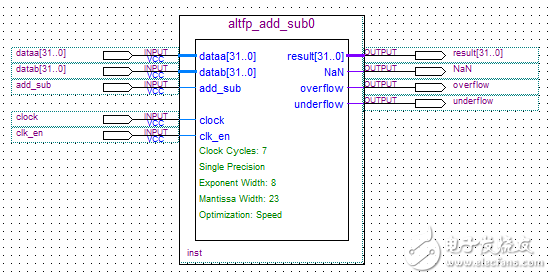

FPGA初学者,想使用Quartus II 中的宏功能模块altfp_add_sub(单精度)实现浮点数加减法。

仿真测试结果有时正确,有时不正确,希望论坛里的大神可以指点一二。

输入的两个数据均以IEEE754标准将十进制数字转换完毕

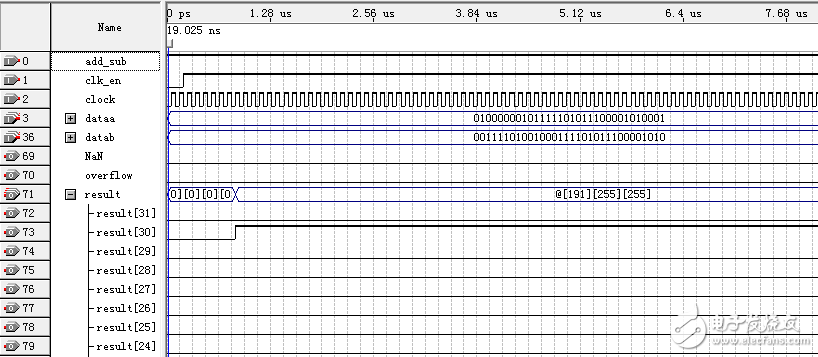

如:0.7839+4.25=5.0339仿真结果正确

0.7839=0 01111110 100 1000 1010 1101 1010 1011

4.25=0 10000001 000 1000 0000 0000 0000 0000

5.0339=0 10000001 010 0001 0001 0101 1011 0101

如:5.96+0.04=6仿真结果错误

5.96=0 10000001 0111 1101 0111 0000 1010 001

0.04=0 01111010 0100 0111 1010 1110 0001 010

结果应该是6=0 10000001 1000 0000 0000 0000 0000 000

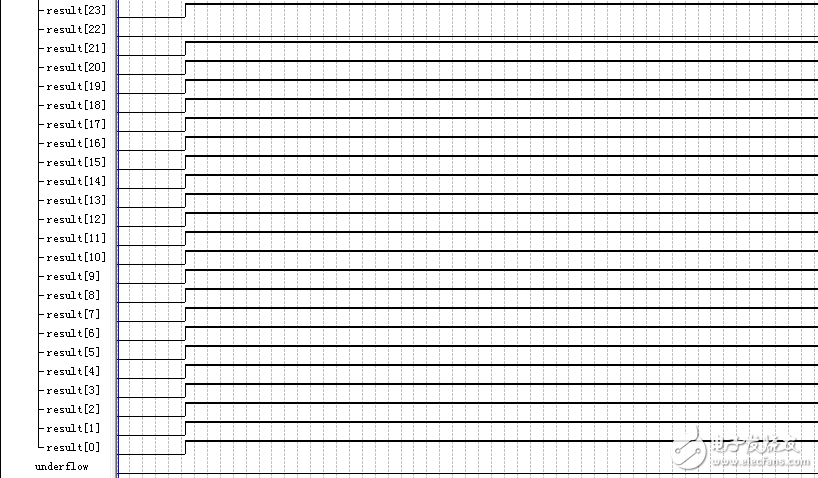

但是仿真结果却是0 10000001 0111 1111 1111 1111 1111 111

仿真结果与真是值小数位置差1

问题出在哪里,希望论坛里的大神们可以指点一二,不胜感激!

仿真测试结果有时正确,有时不正确,希望论坛里的大神可以指点一二。

输入的两个数据均以IEEE754标准将十进制数字转换完毕

如:0.7839+4.25=5.0339仿真结果正确

0.7839=0 01111110 100 1000 1010 1101 1010 1011

4.25=0 10000001 000 1000 0000 0000 0000 0000

5.0339=0 10000001 010 0001 0001 0101 1011 0101

如:5.96+0.04=6仿真结果错误

5.96=0 10000001 0111 1101 0111 0000 1010 001

0.04=0 01111010 0100 0111 1010 1110 0001 010

结果应该是6=0 10000001 1000 0000 0000 0000 0000 000

但是仿真结果却是0 10000001 0111 1111 1111 1111 1111 111

仿真结果与真是值小数位置差1

问题出在哪里,希望论坛里的大神们可以指点一二,不胜感激!

因为你的两个加数在用ieee-754规格化表示的时候,是约数的形式,所以的得到的结果也是不准确的